### **Features**

- Eight Low-Noise PGAs and Eight High-Resolution ADCs

- Input-Referred Noise: 4 μVPP (150 Hz BW, G = 6)

- Input Bias Current: 200 pA

- Data Rate: 250 SPS to 32 kSPS

- CMRR: -115 dB

- Programmable Gain: 1, 2, 3, 4, 6, 8,12 or 24

- Unipolar or Bipolar Supplies:

- AVDD = 2.7 V to 5.5 V

- DVDD = 1.7 V to 3.3 V

- Built-In Right Leg Drive Amplifier, Lead-Off Detection, Wilson Center Terminal, Pace Detection, Test Signals

- Integrated Respiration Impedance Measurement

- Digital Pace Detection Capabilit

- Built-In Oscillator and Reference

- SPI™-Compatible Serial Interface

- ADS1298 Pin Compatible and Program Compatible"

- Operating Temperature Range: -40 °C to +85 °C"

### **Applications**

- Medical Instrumentation (ECG, EMG, and EEG)

- Patient Monitoring; Holter, Event, Stress, and Vital Signs Including ECG,

- AED, Telemedicine Bispectral Index (BIS),

- Evoked Audio Potential (EAP), Sleep Study Monitor

### **General Description**

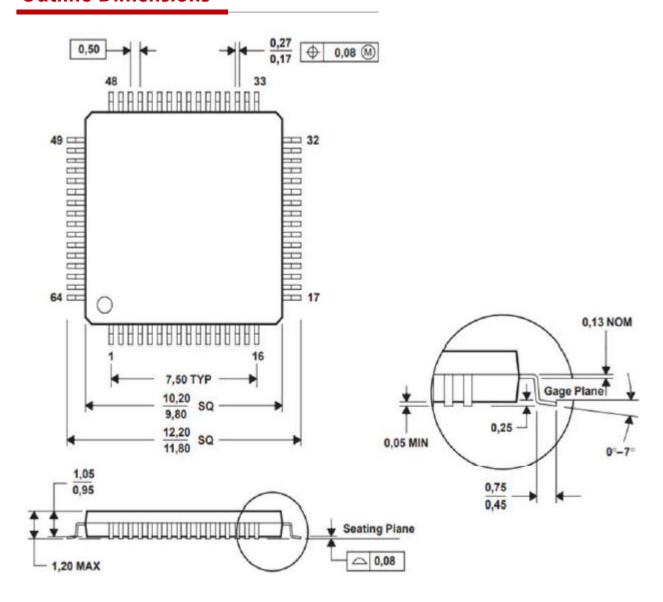

The CBM24AD98Q chip is a low-noise, 24-bit synchronized sampling  $\Delta$ - $\Sigma$  analog-to-digital converter (ADC), featuring an integrated programmable gain amplifier (PGA), internal voltage reference, and internal oscillator. The CBM24AD98Q encompasses all common functionalities required for electrocardiogram (ECG) and extracranial electroencephalogram (EEG) applications. With its high level of integration and superior performance, the CBM24AD98Q enables the creation of scalable medical instrumentation systems with significantly reduced size, power consumption, and overall cost. Each channel of the CBM24AD98Q includes a flexible input multiplexer, which can be independently connected to internally generated signals for testing, temperature measurements, and lead-off detection. Furthermore, the chip allows for flexible configuration in generating the right leg drive signal. Integrated within the chip are three amplifiers used to generate the Wilson Central Terminal (WCT) and Goldberger Central Terminal (GCT) required for standard 12-lead ECGs.The CBM24AD98Q supports both low-power and high-precision modes, with data sampling rates ranging from 250 samples per second (SPS) up to 32 kilosamples per second (kSPS). For high-channel count systems, multiple CBM24AD98Q chips can be cascaded in a daisy-chain configuration. The CBM24AD98Q is available in either a TQFP-64 package (10mm10mm) or a QFN-64 package (9mm9mm), with an operating temperature range rated from -40°C to +85°C.

# Catalog

| Features                                      | J  |

|-----------------------------------------------|----|

| Applications                                  | 1  |

| General Description.                          | 2  |

| Catalog                                       | 3  |

| Functional Block Diagram                      |    |

| Product comparison.                           | 5  |

| Pin configuration and functions.              | 5  |

| Absolute Maximum Ratings                      | 8  |

| ESD                                           | 9  |

| Recommended Operating conditions              | 9  |

| Thermal information                           | 10 |

| Electrical characteristics.                   | 10 |

| Timing requirement: SPI serial interface.     | 14 |

| Switch characteristics: SPI serial interface. | 15 |

| Parameter measurement information.            | 16 |

| Detailed Description                          | 17 |

| Function Description.                         | 17 |

| Product Function Mode                         | 37 |

| Register Definition                           | 48 |

| Applications Matters                          | 66 |

| Outline Dimensions.                           | 66 |

| Package/Ordering Information.                 | 67 |

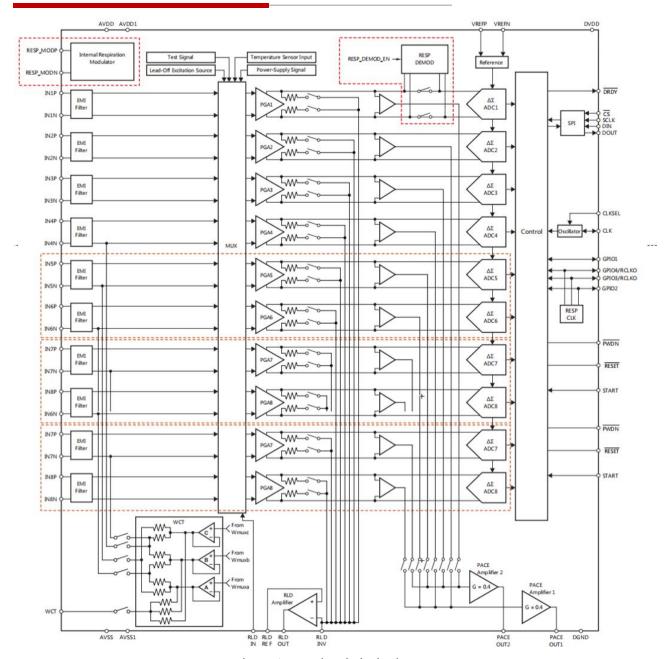

## **Functional Block Diagram**

Figure 1. Functional Block Diagram

## **Product comparison**

| Model      | Package | Temperature | Channel | Resolution | Maximum sampling rate |

|------------|---------|-------------|---------|------------|-----------------------|

| CBM24AD99Q | TQFP-64 | -40°C~85°C  | 8       | 24         | 16kSPS                |

| CBM24AD98Q | TQFP-64 | -40°C~85°C  | 8       | 24         | 32kSPS                |

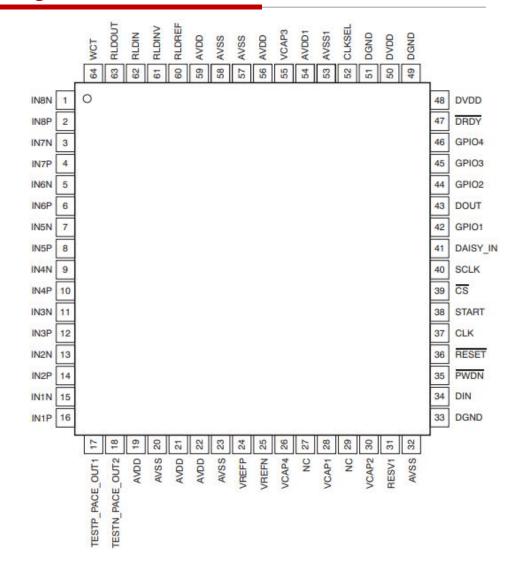

## Pin configuration and functions

|                    | PIN            | ТҮРЕ                    | DESCRIPTION                                           |

|--------------------|----------------|-------------------------|-------------------------------------------------------|

| NO.                | NAME           | ITPE                    | DESCRIPTION                                           |

| AVDD               | 19,21,22,56,59 | Supply                  | Analog supply                                         |

| AVDD               | 59             | Supply                  | Analog supply                                         |

| AVDD1              | 54             | Supply                  | Analog supply                                         |

| AVSS               | 20,23,32,57    | Supply                  | Analog supply                                         |

| AVJJ               | 58             | Supply                  | Analog supply                                         |

| AVSS1              | 53             | Supply                  | Analog supply                                         |

| BIASIN<br>/RLDIN   | 62             | Analog input            | Right leg drive input to mux                          |

| BIASINV/<br>RLDINV | 61             | Analog<br>input/output  | Right leg drive inverting input                       |

| BIASOUT/<br>RLDOUT | 63             | Analog output           | Right leg drive output                                |

| BIASREF/<br>RLDREF | 60             | Analog input            | Right leg drive noninverting input                    |

| CS/CS_             | 39             | Digital input           | SPI chip select; active low                           |

| CLK                | 37             | Digital input           | External Master clock input or internal clock output. |

| CLKSEL             | 52             | Digital input           | Master clock select                                   |

| DAISY_IN           | 41             | Supply                  | Daisy-chain input; if not used, short to DGND.        |

| DGND               | 33,49,51       | Digital input           | Digital ground                                        |

| DIN                | 34             | Digital input           | SPI data input                                        |

| DOUT               | 43             | Digital output          | SPI data output                                       |

| DRDY/DR<br>DY_     | 47             | Digital output          | Data ready; active low                                |

| DVDD               | 48,50          | Supply                  | Digital power supply                                  |

| GPIO1              | 42             | Digital input/output    | General-purpose input/output pin 1                    |

| GPIO2              | 44             | Digital<br>input/output | General-purpose input/output pin 2                    |

| GPIO3              | 45             | Digital<br>input/output | General-purpose input/output pin 3                    |

| GPIO4         | 46    | Digital input/output | General-purpose input/output pin 4                                               |

|---------------|-------|----------------------|----------------------------------------------------------------------------------|

| IN1N          | 15    | Analog input         | Differential analog negative input 1                                             |

| IN1P          | 16    | Analog input         | Differential analog positive input 1                                             |

| IN2N          | 13    | Analog input         | Differential analog negative input 2                                             |

| IN2P          | 14    | Analog input         | Differential analog positive input 2                                             |

| IN3N          | 11    | Analog input         | Differential analog negative input                                               |

| IN3P          | 12    | Analog input         | Differential analog positive input 3                                             |

| IN4N          | 9     | Analog input         | Differential analog negative input 4                                             |

| IN4P          | 10    | Analog input         | Differential analog positive input 4                                             |

| IN5N          | 7     | Analog input         | Differential analog negative input 5(limited to CBM24AD98Q-6 and CBM24AD98Q)     |

| IN5P          | 8     | Analog input         | Differential analog positive input 5(limited to CBM24AD98Q-6 and CBM24AD98Q)     |

| IN6N          | 5     | Analog input         | Differential analog negative input 6(limited to CBM24AD98Q-6 and CBM24AD98Q)     |

| IN6P          | 6     | Analog input         | Differential analog positive input 6(limited to CBM24AD98Q-6 and CBM24AD98Q)     |

| IN7N          | 3     | Analog input         | Differential analog negative input 7(limited to CBM24AD98Q)                      |

| IN7P          | 4     | Analog input         | Differential analog positive input 7(limited to CBM24AD98Q)                      |

| IN8N          | 1     | Analog input         | Differential analog negative input 8(limited to CBM24AD98Q)                      |

| IN8P          | 2     | Analog input         | Differential analog positive input 8(limited to CBM24AD98Q)                      |

| NC            | 27,29 |                      | No connection, can be connected to AVDD or AVSS with a $10$ - $k\Omega$ resistor |

| WCT           | 64    | Analog output        | Wilson Central Terminal output                                                   |

| RESET/RE SET_ | 36    | Digital input        | System-reset pin; active low                                                     |

| RESV1         | 31    | Digital input        | Reserved for future use; must tie to logic low (DGND).                           |

| SCLK                  | 40 | Digital input          | SPI clock                                                                                        |

|-----------------------|----|------------------------|--------------------------------------------------------------------------------------------------|

| SRB1/EST P_PACE_O UT1 | 17 | Analog<br>input/output | Internal test signal/single-ended buffer output based on register settings                       |

| SRB2/EST P_PACE_O UT2 | 18 | Analog<br>input/output | Internal test signal/single-ended buffer output based on register settings                       |

| START                 | 38 | Digital input          | Start conversion                                                                                 |

| PWDN/P<br>WDN_        | 35 | Digital input          | Power-down pin; active low                                                                       |

| VCAP1                 | 28 | Analog output          | Analog bypass capacitor; connect 22-µF capacitor to AVSS                                         |

| VCAP2                 | 30 | Analog output          | Analog bypass capacitor; connect 1-µF capacitor to AVSS                                          |

| VCAP3                 | 55 | Analog output          | Analog bypass capacitor; internally generated AVDD + 1.9 V; connect 1- $\mu$ F capacitor to AVSS |

| VCAP4                 | 26 | Analog output          | Analog bypass capacitor; connect 1-µF capacitor to AVSS                                          |

| VREFN                 | 25 | Analog input           | Negative reference voltage                                                                       |

| VREFP                 | 24 | Analog<br>input/output | Positive reference input/output voltage                                                          |

# **Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                            | MIN      | MAX      | UNIT |

|----------------------------|----------|----------|------|

| AVDD to AVSS               | -0.3     | 5.5      | V    |

| DVDD to DGND               | -0.3     | 3.9      | V    |

| AVSS to DGND               | -3       | 0.2      | V    |

| VREFP input to AVSS        | AVSS-0.3 | AVDD+0.3 | V    |

| Analog input voltage       | AVSS-0.3 | AVDD+0.3 | V    |

| Digital input voltage      | DGND-0.3 | DVDD+0.3 | V    |

| Digital output voltage     | DGND-0.3 | DVDD+0.3 | V    |

| Input current (momentary)  |          | 100      | mA   |

| Input current (continuous) |          | 10       | mA   |

OPERATION INSTRUCTION

| Junction temperature, TJ  | -40 | 150 | °C |

|---------------------------|-----|-----|----|

| Storage temperature, Tstg | -60 | 150 | °C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### **ESD**

|                                            |                                                                              |       | UNIT |

|--------------------------------------------|------------------------------------------------------------------------------|-------|------|

|                                            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins(1)              | ±2000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins(2) | ±500  | V    |

### **Recommended Operating conditions**

over operating ambient temperature range (unless otherwise noted)

|                                           |                                   | MIN           | NOM   | MAX  | UNIT |

|-------------------------------------------|-----------------------------------|---------------|-------|------|------|

| POWER SUPPLY                              |                                   |               |       |      |      |

| Analog power supply (AVDD - AVSS)         |                                   | 2.7           | 3     | 5.25 | V    |

| Digital power supply (DVDD)               |                                   | 1.65          | 1.8   | 3.6  | V    |

| AVDD - DVDD                               |                                   | -2.1          |       | 3.6  | V    |

| ANALOG INPUTS                             |                                   |               |       |      |      |

| Full-scale differential input voltage ran | nge (AINP – AINN)                 | ±VREF / Gain  |       |      | V    |

| Common-mode input voltage                 |                                   | See the 9.3.3 |       |      |      |

| VOLTAGE REFERENCE INPUTS                  |                                   |               |       |      |      |

| Differential reference valte as           | 3-V supply VREF = (VREFP - VREFN) |               | 2.5   |      | V    |

| Differential reference voltage            | 5-V supply VREF = (VREFP - VREFN) |               | 4     |      | V    |

| Negative input (VREFN)                    |                                   |               | AVSS  |      | V    |

| Desiring insulated (ADEED)                |                                   |               | AVSS  |      |      |

| Positive input (VREFP)                    |                                   |               | + 2.5 |      | V    |

| CLOCK INPUT                               |                                   |               |       |      |      |

| External clock input frequency            | CLKSEL pin = 0                    | 1.94          | 2.048 | 2.25 | MHz  |

| DIGITAL INPUTS              |                  |     |  |    |    |  |

|-----------------------------|------------------|-----|--|----|----|--|

| Input Voltage DGND DVDD V   |                  |     |  |    | V  |  |

| TEMPERATURE RANGE           |                  |     |  |    |    |  |

| Commercial grade            |                  |     |  | 70 | °C |  |

| Operating temperature range | Industrial grade | -40 |  | 85 | °C |  |

### **Thermal information**

|                      | THERMAL METRIC(4)                                  | CBM24AD98Q      | 11*4 |

|----------------------|----------------------------------------------------|-----------------|------|

|                      | THERMAL METRIC(1)                                  | PAG(TQFP) 64PIN | Unit |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance             | 46.2            | °C/W |

| $R_{\theta JC(TOP)}$ | Junction-to-case (top) thermal resistance          | 5.8             | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance               | 19.6            | °C/W |

| ψл                   | Junction-to-top characterization parameter         | 0.2             | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter       | 19.2            | °C/W |

| $R_{\theta JC(bot)}$ | Connected to the shell (bottom) thermal resistance | Not applicable  | °C/W |

### **Electrical Characteristics**

Min and max specifications apply for all commercial grade ( $T_A = 0^{\circ}\text{C}$  to  $70^{\circ}\text{C}$ ) devices, and from TA =  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  for industrial-grade devices. Typical specifications at  $T_A = 25^{\circ}\text{C}$ . All specifications at DVDD = 1.8 V, AVDD - AVSS = 3 V (1) ,  $V_{REF} = 2.4 \text{ V}$ , external  $f_{CLK} = 2.048 \text{ MHz}$ , data rate = 500 SPS, HR mode(2) , and gain = 6 (unless otherwise noted).

| Parameter          | Test Conditions                        | Min  | Тур.       | Max  | Unit |  |  |

|--------------------|----------------------------------------|------|------------|------|------|--|--|

| ANALOG INPUTS      |                                        |      |            |      |      |  |  |

| Input capacitance  |                                        |      | 20         |      | pF   |  |  |

|                    | T <sub>A</sub> = 25°C, input = 1.5 V   |      |            | ±200 | рА   |  |  |

| Input bias current | $T_A = 0$ °C to 70°C, input = 1.5 V    |      | ±1         |      | nA   |  |  |

|                    | $T_A = -40$ °C to +85°C, input = 1.5 V |      | ±1.2       |      | nA   |  |  |

|                    | No lead-off                            | 1000 |            |      | МΩ   |  |  |

| DC input impedance | Current source lead-off detection      |      | 500        |      | МΩ   |  |  |

|                    | Pullup resistor lead-off detection     |      | 10         |      | МΩ   |  |  |

| PGA PERFORMANCE    |                                        |      |            |      |      |  |  |

| Gain settings      |                                        | 1,   | 2,3,4,6,8, | 12   |      |  |  |

| Bandwidth                         |                                           | olain |          |         |              |

|-----------------------------------|-------------------------------------------|-------|----------|---------|--------------|

| ADC PERFORMANCE                   |                                           |       |          |         |              |

|                                   | Data rates up to 8 kSPS, no missing codes | 24    |          |         | Bits         |

| Resolution                        | 16-kSPS data rate                         | 19    |          |         | Bits         |

|                                   | 32-kSPS data rate                         | 17    |          |         | Bits         |

| Data vata                         | f <sub>CLK</sub> = 2.048 MHz, HR mode     | 500   |          | 32000   | SPS          |

| Data rate                         | f <sub>CLK</sub> = 2.048 MHz, LP mode     | 250   |          | 16000   | SPS          |

| DC CHANNEL PERFORMA               | ANCE                                      |       |          |         |              |

| Gain = 6 (3) , 10 seconds of data |                                           |       | 5        |         | $\mu V_{PP}$ |

| Input referred poice              | Gain = 6, 256 points, 0.5 seconds of dat  |       | 4        | 7       | $\mu V_{PP}$ |

| Input-referred noise              | Gain settings ≠ 6, data rates≠ 500 SPS    |       |          |         |              |

|                                   | .,                                        | Meası | urements | section |              |

|                                   | Full-scale with gain = 6, best fit        |       | 8        |         | ppm          |

|                                   | Full-scale with gain = 6, best            |       | 10       |         |              |

| Integral nonlinearity(4           | fit,CBM24AD98Q channel 1                  |       | 40       |         | ppm          |

|                                   | -20 dBFS with gain = 6, best              |       | 8        |         | nnm          |

|                                   | fit,CBM24AD98Q channel 1                  |       | 0        |         | ppm          |

| Offset error                      |                                           |       | ±500     |         | μV           |

| Offset error drift                |                                           |       | 2        |         | μV/°C        |

| Gain error                        | Excluding voltage reference error         |       | ±0.2     | ±0.5    | %of FS       |

| Gain drift                        | Excluding voltage reference drift         |       | 5        |         | ppm/°C       |

| Gain match between                |                                           |       | 0.3      |         | %of FS       |

| channels                          |                                           |       | 0.5      |         | 7001 FS      |

- (1) Performance is applicable for 5-V operation as well. Production testing for limits is performed at 3 V.

- (2) LP mode = low-power mode.

- (3) Noise data measured in a 10-second interval. Test not performed in production. Input-referred noise is calculated with input shorted (without electrode resistance) over a 10-second interval.

- (4) The presence of internal demodulation circuitry on channel 1 causes degradation of INL and THD. The effect is pronounced for full-scale signals and is less for small ECG-type signals.

| Parameter Test Conditions Min Typ. Max Unit |

|---------------------------------------------|

|---------------------------------------------|

| LEAD-OFF DETECT                         |                                               |                          |            |

|-----------------------------------------|-----------------------------------------------|--------------------------|------------|

| Frequency                               | See Table 1 for settings                      | <br>0,f <sub>DR</sub> /  | <br>kHz    |

| Current                                 | See Table 16 for settings                     | <br>6,12,1<br>8,24       | <br>nA     |

| Current accuracy                        |                                               | <br>±20%                 |            |

| Comparator threshold accuracy           |                                               | <br>±30                  | <br>mV     |

| EXTERNAL REFERENCE                      |                                               |                          |            |

| Input impedance                         |                                               | <br>10                   | <br>kΩ     |

| INTERNAL REFERENCE                      |                                               |                          |            |

| Output valtage                          | Register bit CONFIG3.VREF_4V = 0,AVDD ≥ 2.7 V | <br>2.4                  | <br>V      |

| Output voltage                          | <br>4                                         | <br>V                    |            |

| V <sub>REF</sub> accuracy               |                                               | <br>±<br>0.2%            |            |

|                                         | TA = 25°C                                     | <br>35                   | <br>ppm/°0 |

| Internal reference drift                | Commercial grade, 0°C to 70°C                 | <br>35                   | <br>ppm    |

|                                         | Industrial grade, –40°C to 85°C               | <br>45                   | <br>ppm    |

| Start-up time                           |                                               | <br>150                  | <br>ms     |

| SYSTEM MONITORS                         |                                               |                          |            |

| Analog-supply reading error             |                                               | <br>2%                   |            |

| Digital-supply reading error            |                                               | <br>2%                   |            |

| Davidas vastas vas                      | From power up to DRDY low                     | <br>150                  | <br>ms     |

| Device wake up                          | STANDBY mode                                  | <br>9                    | <br>ms     |

| Temperature-sensor reading,voltage      | TA = 25° C                                    | <br>145                  | <br>mV     |

| Temperature-sensor reading, coefficient |                                               | <br>490                  | <br>μV/°C  |

| Test-signal frequency                   |                                               | <br>f <sub>CLK</sub> / 2 | <br>Hz     |

|                                       |                                                                            |              | f <sup>CLK</sup> / 2 <sup>20</sup> |              |     |

|---------------------------------------|----------------------------------------------------------------------------|--------------|------------------------------------|--------------|-----|

| Test-signal voltage                   |                                                                            |              | ±1,±2                              |              | mV  |

| Test-signal accuracy                  |                                                                            |              | ±2%                                |              |     |

| CLOCK                                 |                                                                            |              |                                    |              |     |

| Internal-oscillator clock frequency   | Nominal frequency                                                          |              | 2.048                              |              | MHz |

|                                       | TA = 25°C                                                                  |              |                                    | ±0.5%        |     |

| Internal clock accuracy               | 0°C ≤ T <sub>A</sub> ≤ 70°C                                                |              |                                    | ±2%          |     |

| internal clock accuracy               | $-40$ °C $\leq$ T <sub>A</sub> $\leq$ 85°C, industrial grade versions only | -            |                                    | ±2.5%        |     |

| Internal-oscillator start-up time     |                                                                            |              |                                    | 20           | μs  |

| Internal-oscillator power consumption |                                                                            |              | 120                                |              | μW  |

| DIGITAL INPUT/OUTPUT (D               | VVDD = 1.65 V to 3.6 V)                                                    |              |                                    |              |     |

| VIH High-level inpout voltage         |                                                                            | 0.8D<br>VDD  |                                    | DVDD<br>+0.1 | V   |

| VIL Low-level input voltage           |                                                                            | -0.1         |                                    | 0.2DV<br>DD  | V   |

| VOH High-level output<br>voltage      | I <sub>OH</sub> = -500 μA                                                  | DVD<br>D-0.4 |                                    |              | V   |

| VOL Low-level output<br>voltage       | I <sub>O</sub> L = 500 μA                                                  |              | -                                  | 0.4          | V   |

| IIN Input current                     | 0 V < V <sub>DigitalInput</sub> < DVDD                                     | -10          |                                    | 10           | μΑ  |

| POWER SUPPLY (RLD, WCT,               | AND PACE AMPLIFIERS TURNED OFF) H                                          |              |                                    |              |     |

|                                       | AVDD – AVSS = 3 V,HR mode                                                  |              | 2.75                               |              | mA  |

| I AV/DD current                       | AVDD – AVSS = 3 V,LP mode                                                  |              | 1.8                                |              | mA  |

| I <sub>AVDD</sub> AVDD current        | AVDD – AVSS = 5 V,HR mode                                                  |              | 3.1                                | -            | mA  |

|                                       | AVDD – AVSS = 5 V,LP mode                                                  |              | 2.1                                |              | mA  |

|                                       | DVDD = 1.8V,HR mode                                                        |              | 0.3                                |              | mA  |

| I <sub>DVDD</sub> DVDD current        | DVDD = 1.8V,LP mode                                                        |              | 0.3                                |              | mA  |

|                                       | DVDD = 3V,HR mode                                                          |              | 0.5                                |              | mA  |

|                         | DVDD = 3V,LP mode    |                                |   | 0.5  |     | mA |

|-------------------------|----------------------|--------------------------------|---|------|-----|----|

|                         | CBM24AD98Q、          | HR mode                        |   | 8.8  | 9.5 | mW |

|                         | AVDD-AVSS = 3V       | LP mode(250SPS)                |   | 6.0  | 7.0 | mW |

|                         | CBM24AD98Q-6、        | HR mode                        |   | 7.2  | 7.9 | mW |

|                         | AVDD-AVSS = 3V       | LP mode(250SPS)                |   | 5.3  | 6.6 | mW |

|                         | CBM24AD98Q-4、        | HR mode                        |   | 5.4  | 6   | mW |

|                         | AVDD-AVSS = 3V       | LP mode(250SPS)                |   | 4.1  | 4.4 | mW |

| Power dissipation       | CBM24AD98Q、          | HR mode                        |   | 17.5 |     | mW |

|                         | AVDD-AVSS = 5V       | LP mode(250SPS)                |   | 12.5 |     | mW |

|                         | CBM24AD98Q-6、        | HR mode                        |   | 14.1 |     | mW |

|                         | AVDD-AVSS = 5V       | LP mode(250SPS)                |   | 10   |     | mW |

|                         | CBM24AD98Q-4、        | HR mode                        |   | 10.1 |     | mW |

|                         | AVDD-AVSS = 5V       | AVDD-AVSS = 5V LP mode(250SPS) |   | 8.3  |     | mW |

| Power-down              | AVDD - AVSS = 3 V    |                                |   | 10   |     | μW |

| Power-down              | AVDD - AVSS = 5 V    |                                |   | 20   |     | μW |

| Ctandby made            | AVDD - AVSS = 3 V    |                                | 2 |      | mW  |    |

| Standby mode            | AVDD - AVSS = 5 V    |                                | 4 |      | mW  |    |

| Quiescent channel power | AVDD - AVSS = 3 V, I | PGA + ADC                      |   | 818  |     | μW |

| Quiescent channel power | AVDD - AVSS = 5 V, I | PGA + ADC                      |   | 1.5  |     | mW |

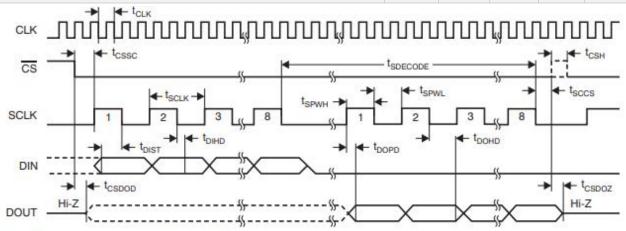

# **Timing requirement: SPI serial interface**

Specifications apply from TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C (unless otherwise noted); load on DOUT = 20 pF || 100 k $\Omega$

|                                                              | 2.7 V ≤ | DVDD | 1.65 V | ≤    |    |

|--------------------------------------------------------------|---------|------|--------|------|----|

|                                                              | ≤ 3.6 V |      | DVDD   | UNIT |    |

|                                                              | MIN     | MAX  | MIN    | MAX  |    |

| t <sub>CLK</sub> Master clock period                         | 414     | 514  | 414    | 514  | ns |

| t <sub>CSSC</sub> CS low to first SCLK, setup time           | 6       |      | 17     |      | ns |

| t <sub>SCLK</sub> SCLK period                                | 50      |      | 66.6   |      | ns |

| S <sub>PWH, L</sub> SCLK pulse width, high and low           | 15      |      | 25     |      | ns |

| t <sub>DIST</sub> DIN valid to SCLK falling edge: setup time | 10      |      | 10     |      | ns |

| t <sub>DIHD</sub> Valid DIN after SCLK falling edge: hold time         | 10 | <br>11 | <br>ns               |

|------------------------------------------------------------------------|----|--------|----------------------|

| t <sub>CSH</sub> CS high pulse                                         | 2  | <br>2  | <br>t <sub>CLK</sub> |

| t <sub>SCCS</sub> Eighth SCLK falling edge to CS high                  | 4  | <br>4  | <br>t <sub>CLK</sub> |

| t <sub>SDECODE</sub> Command decode time                               | 4  | <br>4  | <br>t <sub>CLK</sub> |

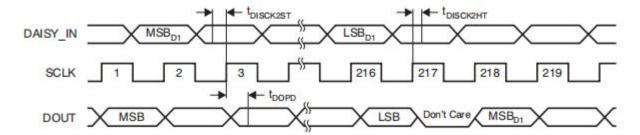

| t <sub>DISCK2ST</sub> DAISY_IN valid to SCLK rising edge: setup time   | 10 | <br>10 | <br>ns               |

| t <sub>DISCK2HT</sub> DAISY_IN valid after SCLK rising edge: hold time | 10 | <br>10 | <br>ns               |

### Switch characteristics: SPI serial interface

Specifications apply from  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (unless otherwise noted). Load on DOUT = 20 pF || 100 k $\Omega$ .

|                    |                                              | 2.7 V ≤ DVDD<br>≤ 3.6 V |     |     | 1.65 V ≤   |    |  |

|--------------------|----------------------------------------------|-------------------------|-----|-----|------------|----|--|

|                    | PARAMETER                                    |                         |     |     | DVDD ≤ 2 V |    |  |

|                    |                                              | MIN                     | MAX | MIN | MAX        |    |  |

| t <sub>DOHD</sub>  | SCLK falling edge to invalid DOUT: hold time | 10                      |     | 10  |            | ns |  |

| t <sub>DOPD</sub>  | SCLK rising edge to DOUT valid: setup time   |                         | 17  |     | 32         | ns |  |

| t <sub>CSDOD</sub> | CS low to DOUT driven                        | 10                      |     | 20  |            | ns |  |

| t <sub>CSDOZ</sub> | CS high to DOUT Hi-Z                         |                         | 10  |     | 20         | ns |  |

NOTE: SPI settings are CPOL = 0 and CPHA = 1.

Figure 7.1. Serial Interface Timing

Figure 7.2. Daisy-Chain Interface Timing

### **Parameter measurement information**

#### **Noise measurement**

Optimizing the noise performance of the CBM24AD98Q channel can be achieved by adjusting the data rate and PGA gain. Both reducing the data rate and increasing the PGA gain lead to a reduction in input noise, which is particularly beneficial for measuring weak bioelectric potential signals. The following table presents the noise performance measurements of the CBM24AD98Q under conditions of a 5V analog supply and a 4.5V reference voltage. These figures represent the typical noise performance at a temperature (TA) of +25°C. The displayed data are the averaged readings from multiple chips and were taken with the input shorted. A minimum of 1,000 consecutive readings were used to compute the RMS ( $\mu$ VRMS) and peak-to-peak ( $\mu$ VPP) noise for each measurement. For lower data rates, the ratio between RMS and peak-to-peak noise is approximately 6.6.

Table 8.1. Input-Referred Noise  $\mu V_{RMS}$  ( $\mu V_{PP}$ ) in High-Resolution Mode 3-V Analog Supply and 2.4-V Reference(1)

| DR BITS OF<br>CONFIG1<br>REGISTER | OUTPUT<br>DATA RATE<br>(SPS) | -3-dB<br>BANDWIDTH<br>(Hz) | PGA<br>GAIN = 1 | PGA<br>GAIN = 2 | PGA<br>GAIN = 3 | PGA<br>GAIN = 4 | PGA<br>GAIN = 6 | PGA<br>GAIN = 8 | PGA<br>GAIN = 12 |

|-----------------------------------|------------------------------|----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| 000                               | 32000                        | 8398                       | 335 (3553)      | 168 (1701)      | 112 (1100)      | 85 (823)        | 58 (529)        | 42.5 (378)      | 28.6 (248)       |

| 001                               | 16000                        | 4193                       | 56 (613)        | 28 (295)        | 18.8 (188)      | 14.3 (143)      | 9.7 (94)        | 7.4 (69)        | 5.2 (44.3)       |

| 010                               | 8000                         | 2096                       | 12.4 (111)      | 6.5 (54)        | 4.5 (37.9)      | 3.5 (29.7)      | 2.6 (21.7)      | 2.2 (17.8)      | 1.8 (13.8)       |

| 011                               | 4000                         | 1048                       | 6.1 (44.8)      | 3.2 (23.3)      | 2.4 (17.1)      | 1.9 (14)        | 1.5 (11.1)      | 1.3 (9.7)       | 1.2 (8.5)        |

| 100                               | 2000                         | 524                        | 4.1 (27.8)      | 2.2 (15.4)      | 1.6 (11)        | 1.3 (9.1)       | 1.1 (7.3)       | 1 (6.5)         | 0.9 (6)          |

| 101                               | 1000                         | 262                        | 2.9 (19)        | 1.6 (10.1)      | 1.2 (7.5)       | 1 (6.2)         | 0.8 (5)         | 0.7 (4.6)       | 0.6 (4.1)        |

| 110                               | 500                          | 131                        | 2.1 (12.5)      | 1.1 (6.8)       | 0.9 (5.1)       | 0.7 (4.3)       | 0.6 (3.5)       | 0.5 (3.1)       | 0.5 (2.9)        |

Table 8.2. Input-Referred Noise  $\mu V_{RMS}$  ( $\mu V_{PP}$ ) in Low-Power Mode 3-V Analog Supply and 2.4-V Reference(1)

| DR BITS OF<br>CONFIG1<br>REGISTER | OUTPUT<br>DATA RATE<br>(SPS) | -3-dB<br>BANDWIDTH<br>(Hz) | PGA<br>GAIN = 1 | PGA<br>GAIN = 2 | PGA<br>GAIN = 3 | PGA<br>GAIN = 4 | PGA<br>GAIN = 6 | PGA<br>GAIN = 8 | PGA<br>GAIN = 12 |

|-----------------------------------|------------------------------|----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| 000                               | 16000                        | 4193                       | 333 (3481)      | 166 (1836)      | 111 (1168)      | 84 (834)        | 56 (576)        | 42 (450)        | 28 (284)         |

| 001                               | 8000                         | 2096                       | 56 (554)        | 28 (272)        | 19 (177)        | 14.3 (133)      | 9.7 (85)        | 7.4 (64)        | 5 (42.4)         |

| 010                               | 4000                         | 1048                       | 12.5 (99)       | 6.5 (51)        | 4.5 (35)        | 3.4 (25.9)      | 2.4 (18.8)      | 2 (14.5)        | 1.5 (11.3)       |

| 011                               | 2000                         | 524                        | 6.1 (41.8)      | 3.2 (22.2)      | 2.3 (15.9)      | 1.8 (12.1)      | 1.4 (9.3)       | 1.2 (7.8)       | 1 (6.7)          |

| 100                               | 1000                         | 262                        | 4.1 (26.3)      | 2.2 (14.6)      | 1.6 (9.9)       | 1.3 (8.1)       | 1 (6.2)         | 0.8 (5.4)       | 0.7 (4.7)        |

| 101                               | 500                          | 131                        | 3 (17.9)        | 1.6 (9.8)       | 1.1 (6.8)       | 0.9 (5.7)       | 0.7 (4.2)       | 0.6 (3.6)       | 0.5 (3.4)        |

| 110                               | 250                          | 65                         | 2.1 (11.9)      | 1.1 (6.3)       | 0.8 (4.6)       | 0.7 (4)         | 0.5 (3)         | 0.5 (2.6)       | 0.4 (2.4)        |

### **Detailed Description**

The CBM24AD98Q is a low-noise, low-power, multi-channel, simultaneous sampling, 24-bit  $\Delta\Sigma$ analog-to-digital converter (ADC) chip, integrating a programmable gain amplifier (PGA) and various EEG-specific functionalities, making it highly suitable for applications such as electrocardiogram (ECG) and electroencephalogram (EEG). By powering down the EEG-specific circuits, these chips can also be utilized in high-performance, multi-channel data acquisition systems. This series of chips boasts a highly configurable multiplexer that facilitates temperature, power supply, input short, and bias measurements. Additionally, the multiplexer enables any input electrode to be programmed as a reference driver. The PGA gain can be selected from seven settings: 1, 2, 4, 6, 8, 12, and 24. The ADC within the chip supports data rates ranging from 250 samples per second (SPS) up to 16 kilosamples per second (kSPS). Communication with the chip is facilitated through an SPI-compatible interface and is complemented by four general-purpose input/output (GPIO) pins. Synchronization of multiple chips can be achieved using the START pin.Internally, a reference generator produces a low-noise 4.5V voltage, while an oscillator generates a 2.048 MHz clock. A versatile patient bias drive module permits the selection of any electrode combination's average to generate the patient-driven signal. Lead-off detection is accomplished via a current source.

### **Function Description**

This section describes the internal functional information of the CBM24AD98Q. Here,  $f_{CLK}$  represents the frequency of the signal on the CLK pin,  $t_{CLK}$  denotes the period of the signal on the CLK pin,  $f_{DR}$  indicates the output data rate,  $t_{DR}$  signifies the output data time cycle, and  $f_{MOD}$  refers to the frequency at which the modulator samples the input.

### **Input Multiplexer**

In the CBM24AD98Q, each channel is equipped with an input multiplexer (depicted in Figure 9.3.1), offering flexible signal routing options through configuration. In the diagram, MAIN signifies the conditions where MUX[2:0] is set to 000, 110, or 111.

Figure 9.3.1 Multiplexer on Channel

- (1) Chip Noise Measurement Setting CHnSET[2:0] to 001 shorts the P/N terminals of the channel and sets a common-mode voltage of [(VVREFP + VVREFN)/2] for both channel inputs. This configuration can be utilized for testing the inherent noise of the chip.

- (2) Test Signal (TestP and TestN) Configuring CHnSET[2:0] to 101 introduces an internally generated test signal to the P/N terminals of the channel. Details regarding the internal test signal can be found in the CONFIG2 register description.

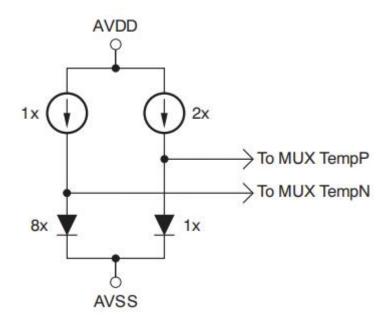

- (3) Temperature Sensor (TempP, TempN) The CBM24AD98Q incorporates an on-chip temperature sensor, which employs two internal diodes, with one diode having a current density sixteen times that of the other, as depicted in Figure 9.3.2. The disparity in diode current densities generates a voltage difference proportional to the absolute temperature. Owing to the low thermal resistance from the package to the printed circuit board (PCB), the internal chip temperature is closely correlated with the PCB temperature. Note that self-heating of the CBM24AD98Q can lead to internal temperature readings higher than the ambient temperature of the surrounding PCB. Setting CHnSET[2:0] to 100 routes the temperature sensor signals to the P/N terminals of the channel.

Figure 9.3.2 Illustration of Temperature Sensor Measurement Inputs

(4) Power Supply Measurement (MVDDP, MVDDN) Setting CHn

SET[2:0] to 011 configures the channel inputs to monitor different supply voltages of the chip. For channels 1, 2, 5, 6, 7, and 8, (MVDDP – MVDDN) equals  $[0.5 \times (AVDD + AVSS)]$ . For channels 3 and 4, (MVDDP – MVDDN) is DVDD / 4. To prevent PGA saturation during power supply measurement, set the gain to 1.

- (5) Lead-Off Excitation Signals (LoffP, LoffN) Lead-off excitation signals are fed into the multiplexer before switching. The comparators detecting lead-off conditions are also connected to the multiplexer prior to switching. For detailed explanation, refer to the Lead-off Detection section. (6) Single-Ended Input Measurement Mode Setting CHnSET[2:0] to 011 or 111 routes the bias signal from the BIASIN pin to the designated electrode, enabling the channel to operate as a single-ended input channel. Setting CHnSET[2:0] to 010 and setting the BIAS\_MEAS bit in the CONFIG3 register to "1" measures the signal on the BIASIN pin relative to the voltage on the BIASREF pin.

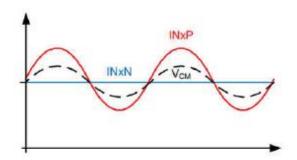

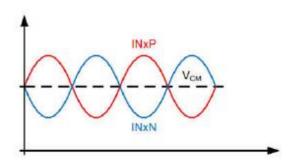

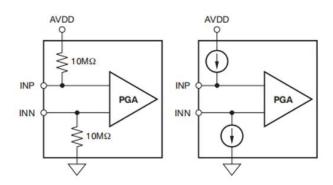

- **9.3.2 Analog Inputs** The analog inputs of the chip are connected to a low-noise, low-drift, high-input impedance programmable gain amplifier via a multiplexer. The CBM24AD98Q analog inputs are fully differential. The range of the differential input voltage (VINxP VINxN) spans from –VREF/Gain to VREF/Gain. There are two methods to drive the analog inputs of the CBM24AD98Q: pseudo-differential or fully differential, as illustrated in Figure 9.3.3.

Figure 9.3.3 Pseudo-Differential (Left) and Fully Differential (Right) Driving Configurations Maintaining the INxN pin at a common voltage, ideally at the mid-supply level, constitutes a pseudo-differential input approach. The INxP pin is then swung around this common voltage between  $-V_{REF}/Gain$  and  $V_{REF}/Gain$ , while staying within the absolute maximum rating specifications. When configured for pseudo-differential mode, the common-mode voltage (VCM) will vary with the signal level changes, requiring that the differential signal at its minimum and maximum satisfy the common-mode input specification.Configuring the signals on INxP and INxN as inverse signals centered around a common-mode voltage (VCM) represents the fully differential input method. Both INxP and INxN inputs swing from a common voltage of +1/2 VREF/Gain to a common voltage of -1/2 VREF/Gain. The differential voltage at the peaks and troughs equals  $-V_{REF}/Gain$  to VREF/Gain, centered around a fixed common-mode voltage. For optimal performance, it is recommended to set the common-mode voltage at the midpoint of the analog supplies, i.e., [(AVDD + AVSS)/2].

### PGA settings and input range

The low-noise PGA is a differential-input and output amplifier whose gain settings (1, 2, 4, 6, 8, 12, and 24) can be configured by writing to the CHnSET register. As the CBM24AD98Q inputs are CMOS-based, current noise can be considered negligible. Table 9.3.1 presents typical bandwidth values for various gain settings. Please note that the table illustrates small-signal bandwidth; for large signals, performance is limited by the PGA's slew rate.

Table 9.3.1 PGA Gain and Bandwidth

| Obtain | Nominal bandwidth at room temperature |

|--------|---------------------------------------|

| Obtain | (kHz)                                 |

| 1      | 662                                   |

| 2      | 332                                   |

| 4      | 165                                   |

| 6      | 110                                   |

| 8      | 83                                    |

| 12 | 55 |

|----|----|

| 24 | 27 |

To maintain operation within the linear range of the PGA, input signals must comply with the following:

AVDD-0.2V-((Gain x V<sub>MAX DIFF</sub>))/2>CM>AVSS+0.2V+((Gain x V<sub>MAX DIFF</sub>))/2

Here,  $V_{MAX\_DIFF}$  denotes the maximum differential input voltage of the PGA; CM represents the common-mode range. For instance: If AVDD = 5 V, Gain = 12, and VMAX\_DIFF = 350 mV, then 2.3 V < CM < 2.7 V. The differential input voltage range (VINxP - VINxN) is dependent on the analog supply and reference voltage used in the system as well as the gain, spanning from - VREF/Gain to VREF/Gain.

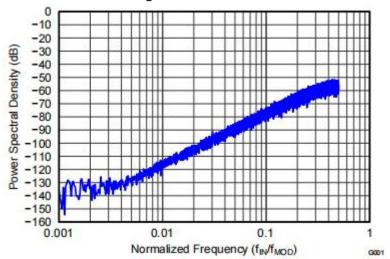

### **ΔΣ** Modulator

Each channel in the CBM24AD98Q features a 24-bit  $\Delta\Sigma$  Analog-to-Digital Converter (ADC). The converter utilizes a second-order modulator optimized for low-noise applications. The modulator samples the input signal at a rate of (fMOD = fCLK/2), with the chip noise being shaped up to fMOD/2, as illustrated in Figure 9.3.4.

Figure 9.3.4 Modulator noise spectrum

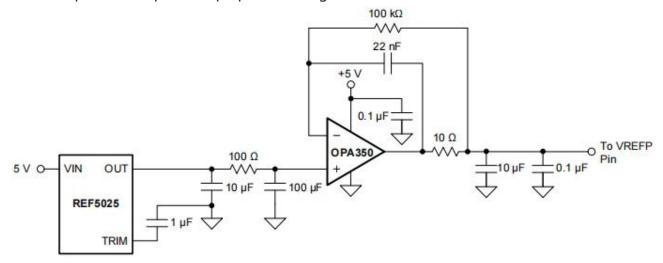

### **Reference Voltage**

The CBM24AD98Q internally generates a reference voltage typically at 4.5V or 2.4V (based on AVSS), controlled by the VREF\_4V bit in the CONFIG3 register. When utilizing the internal reference voltage, VREFN should be connected to AVSS. The internal reference buffer can be disabled, allowing for the application of an external reference to VREFP. Figure 9.3.5 depicts a typical circuit for driving an external reference. The internal reference circuit can be powered down via the PD\_REFBUF bit in the CONFIG3 register. In scenarios where multiple chips are

cascaded, the internal reference of one chip can be shared by powering it down on the others. By default, upon wake-up, the chip operates using an external reference.

Figure 9.3.5 External Reference Driver

### **Digital decimation filter**

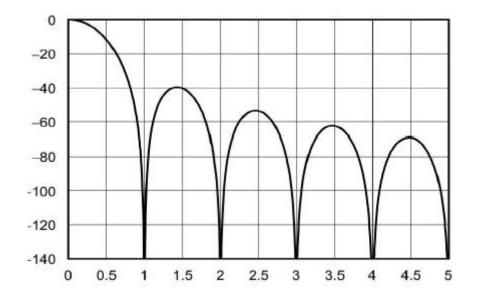

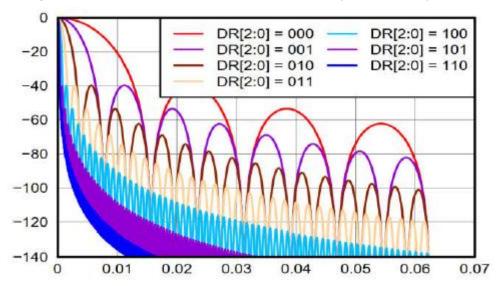

The digital filter receives the modulator output and decimates the data stream. By adjusting the filtering parameters, a trade-off can be made between resolution and data rate: more filtering yields higher resolution, whereas less filtering allows for a higher data rate. Higher data rates are typically employed in EEG applications for AC lead-off detection. The digital filter on each channel comprises a third-order sinc filter. The decimation ratio of the sinc filter can be adjusted via the DR bits in the CONFIG1 register. This setting is a global one affecting all channels, hence all channels in the chip operate at the same data rate. The sinc filter is a third-order low-pass filter with a variable decimation rate. Data enters the filter at the rate of f<sub>MOD</sub> from the modulator, undergoes high-frequency noise filtering, and is then decimated into parallel data at the rate of fDR. The Z-domain transfer function of the sinc filter (with N as the decimation factor) is as follows:

$$|H(z)| = \left| \frac{1 - Z^{-N}}{1 - Z^{-1}} \right|^{3}$$

Figure 9.3.6/7 shows the transmission characteristics of the filter, with normalized frequency on the horizontal axis and gain (dB) on the vertical axis.

Figure 9.3.6 Sinc transmission characteristics (frequency normalized by f<sub>IN</sub>/f<sub>DR</sub>)

Figure 9.3.7 Sinc Filter Transfer Characteristics (Frequency Normalized to f<sub>IN</sub>/f<sub>MOD</sub>)

### Clock

The CBM24AD98Q offers both internal and external clocking methods. The internal clock is suitable for low-power, battery-operated systems, with the oscillator factory-calibrated at room temperature for accuracy. Clock selection is governed by the CLKSEL pin and the CLK\_EN register bit. The CLKSEL pin determines whether the internal or external clock is used. The CLK\_EN bit in the CONFIG1 register enables or disables the oscillator clock to be output on the CLK pin. A truth table for these two controls is provided in Table 9.3.2.

Table 9.3.2 Truth Table for CLKSEL Pin and CLK\_EN Bit

| CLKSEL PIN | CONFIG1.CLK_EN BIT | CLOCK SOURCE              | CLK PIN STATUS                    |  |  |

|------------|--------------------|---------------------------|-----------------------------------|--|--|

| 0          | X                  | External clock            | Input: external clock             |  |  |

| 1          | 0                  | Internal clock oscillator | Tri-state                         |  |  |

| 1          | 1                  | Internal clock oscillator | Output: internal clock oscillator |  |  |

### **General-Purpose Input/Output Interface**

The CBM24AD98Q features four general-purpose digital I/O (GPIO) pins available during normal operation modes. These GPIO pins can be individually configured as inputs or outputs via the GPIOC bit registers. The GPIO level is controlled by the GPIOD bits in the GPIO register. Reading the GPIOD bits returns the logical level of the pin, regardless of whether they are programmed as inputs or outputs. Writing to the GPIOD bits is ineffective when the GPIO pins are configured as inputs. When set as outputs, writing to the GPIOD bits sets the GPIO output value.

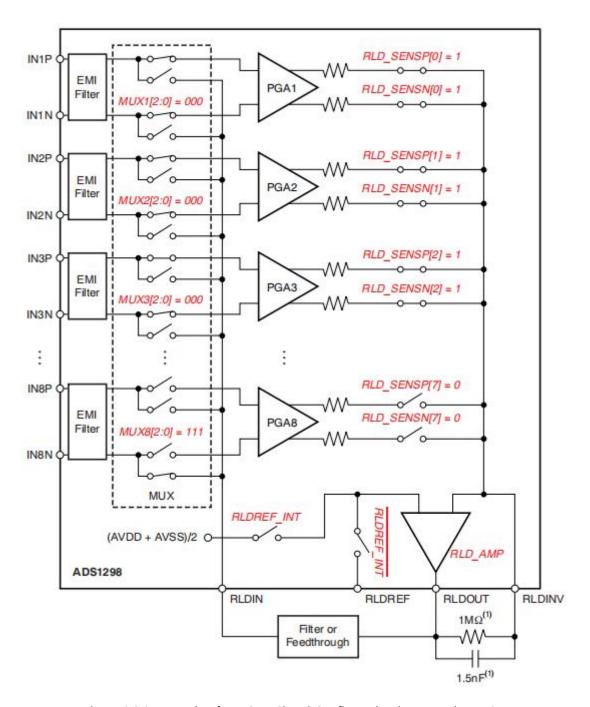

### **Bias (BIAS) Drive Circuit**

Employing a bias (BIAS) drive circuit to stimulate the body helps counteract common-mode interference in EEG systems caused by power lines and other sources, including fluorescent lighting. Figure 9.3.8 illustrates an example of a bias circuit connection. The reference voltage for the bias drive can be internally generated [(AVDD + AVSS)/2] or externally supplied via a resistor divider network. Selection of the bias loop's reference voltage, either internal or external, is defined by writing the appropriate value to the BIASREF\_INT bit in the CONFIG2 register. The BIAS\_SENSEP/N selects the corresponding channel to be connected to the BIASINV terminal of the bias circuit. Upon choosing the appropriate channel, feedback components, and closing the loop externally on the chip, a BIAS bias signal is outputted at the BIASOUT pin. This signal can be fed, after filtering or directly, into the BIASIN pin, as depicted in Figure 9.12. To route this BIASIN signal to the designated input P-side/N-side electrode, the MUX bits in the respective channel setting register must be set to "110" / "111".

Figure 9.3.8. Example of RLDOUT Signal Configured to be Routed to IN8N

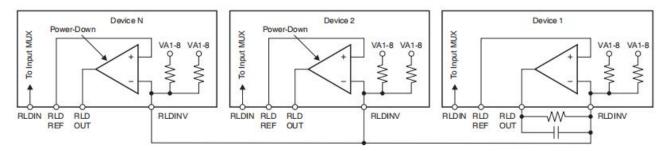

The bias drive functionality can be disabled using the PD\_BIAS bit in the CONFIG3 register. When multiple CBM24AD98Q chips are daisy-chained, the PD\_BIAS bit is used to disable all but one of the bias amplifiers. Figure 9.3.9 demonstrates the setup with multiple chips connected for the bias circuit. When several CBM24AD98Q chips are cascaded in a daisy chain configuration, it's essential to manage the bias amplifiers carefully. By leveraging the PD\_BIAS bit found within the CONFIG3 register, you can selectively deactivate the bias amplifiers in all but one of the

interconnected devices. This ensures that only a single bias amplifier remains operational, which is typically sufficient for driving the bias current through the entire chain of chips. Figure 9.3.9 provides a visual representation of how these multiple chips are connected in relation to the bias circuit, highlighting the importance of proper bias amplifier management in multi-chip setups.

Figure 9.3.9 BIAS driver connections for multiple chips

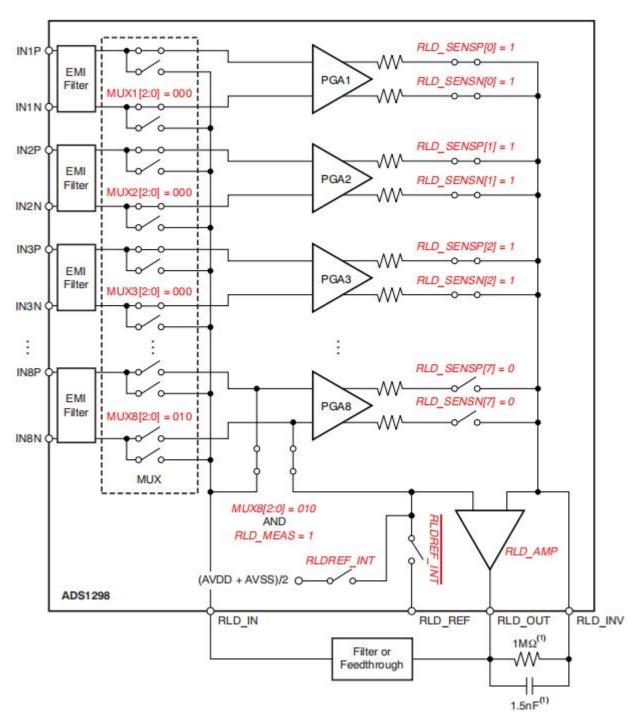

Furthermore, the BIASOUT signal can be routed to a specific channel (not involved in the BIAS computation) for measurement purposes. Figure 3.9.10 illustrates the register settings required to route the BIASIN signal to Channel 8. The measurement is performed relative to the voltage on the BIASREF pin. If BIASREF is selected as internal, then BIASREF equals [(AVDD + AVSS)/2]. This feature can be utilized for debugging purposes during product development.Please note that Figure 3.9.10 was referenced as an illustrative example, but the actual figure content was not provided. The described functionality allows for the monitoring and verification of the BIASOUT signal's integrity and performance by measuring it against a known reference voltage, which is particularly useful during the prototyping and testing phases of product development.

Figure 9.3.10. RLDOUT Signal Configured to be Read Back by Channel 8

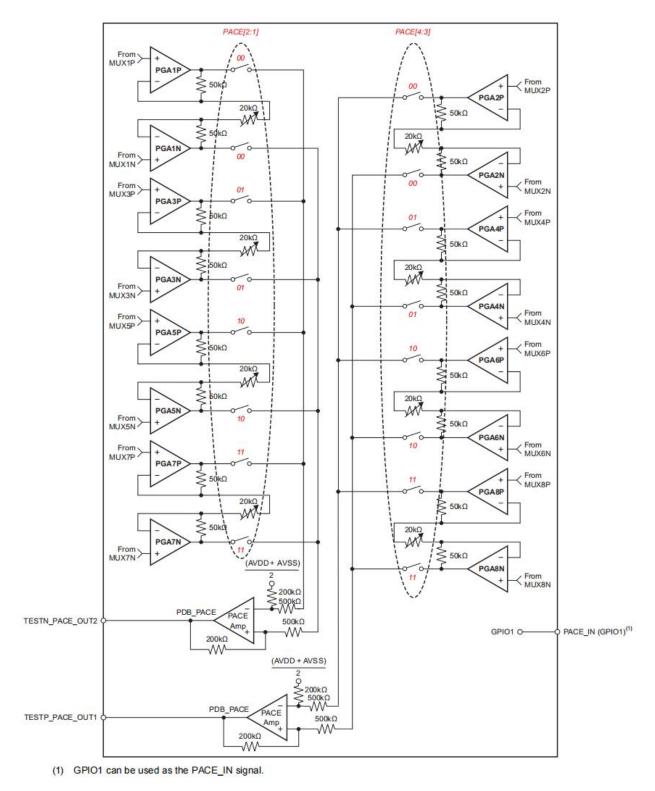

In addition to the BIASOUT signal, which can serve as a reference for single-ended inputs in the CBM24AD98Q, there are also two Stimulus Reference (SRB1/2) signals that can act as references for single-ended inputs. These two signals further double as sensing signals for pacemakers. Figure 9.3.11 depicts the driving circuits for these signals. SRB2 is driven by the odd-numbered channels, and SRB1 by the even-numbered channels, with channel selection governed

### **OPERATION INSTRUCTION**

respectively by the SRB2\_SEL and SRB1\_SEL register bits, detailed in the MISC1 register definition. Note that a 0.4 attenuation exists when converting from differential to single-ended, thus the total gain equals (0.4 × PGA\_GAIN). Unlike BIASOUT, the SRB1/2 signal drivers are internally closed-looped within the chip, enabling direct use without requiring external closed-loop circuits.Regarding SRB1, it can only be routed to the negative end (N-end) of all channels under the control of the SRB1 bit in the MISC1 register, with the signal entering through the positive end (P-end), forming a differential input with SRB1.As for SRB2, it can be directed to the positive end (P-end) of the respective channel by the SRB2 bit in the corresponding CHnSET register of that channel, with the signal entering from the negative end (N-end), thereby creating a differential input with SRB2. It is important to note that the phase of the signal sampled and output after entering from the negative end will be inverted.

Figure 9.3.11 Excitation and Reference (SRB1/2) Drive Circuit

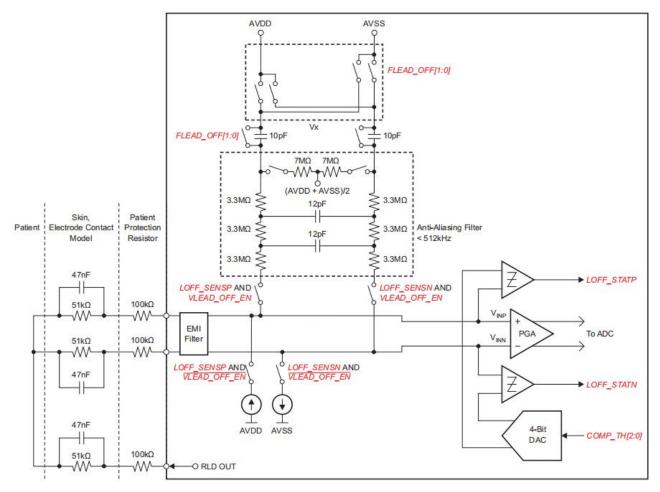

#### **Lead-off Detection (Electrode Disconnection Detection)**

The contact impedance between electrodes and the human body may change over time or during usage, leading to disconnections, necessitating continuous monitoring of the electrode-to-body connection. The CBM24AD98Q features a lead-off detection module designed specifically for this purpose. Although referred to as lead-off detection, it essentially detects electrode detachment. Fundamentally, lead-off detection works by injecting an excitation current and measuring the voltage to ascertain the quality of electrode contact, as illustrated in Figure 9.3.12. The circuitry provides two distinct methods for determining the status of the electrodes, differing primarily in the frequency components of the excitation signal. The leads to be monitored can be selected using the LOFF SENSP and LOFF SENSN registers. The first method involves stimulating the lead with a DC signal. The DC stimulation signal can originate from external pull-up or pull-down resistors or from an internal current source or sink, as shown in Figure 9.3.12. One side of the channel is pulled up to the supply voltage, while the other is pulled down to ground. By setting the corresponding bits in the LOFF\_FLIP register, the pull-up and pull-down currents can be swapped. If a current source is used, the magnitude of the current can be set using the ILEAD OFF[1:0] bits in the LOFF register. Compared to a 10-M $\Omega$  pull-up or pull-down resistor, a current source offers a higher input impedance.

Figure 9.3.12. Lead-Off Detection

The connection status of the leads can be monitored by reading the output code of the channel or by employing an on-chip comparator. Should the electrode become disconnected, the pull-up and pull-down resistances cause the channel to saturate. The comparator monitors the input voltage against a 3-bit DAC level, with the DAC level set by the COMP\_TH[2:0] bits in the LOFF register. The output of the comparator is stored in the LOFF\_STATP and LOFF\_STATN registers. This data forms part of the output data stream. (Refer to the Output Data section for more details.) If DC lead-off detection is not in use, the comparators can be deactivated by setting the PD\_LOFF\_COMP\_ bit in the CONFIG4 register.

Figure 9.3.13 DC lead detachment detection options

Another approach employs an in-band AC signal to stimulate the leads. The AC signal is generated by alternately providing a fixed-frequency current source at the input. The frequency can be selected using the FLEAD\_OFF[1:0] bits in the LOFF register (either 7.8 Hz or 31.2 Hz). This in-band excitation signal is captured through the channel and read at the output. The AC excitation introduces a frequency within the band of interest, which can be filtered and processed separately. The impedance of the electrodes can be calculated by measuring the output amplitude at the frequency of the excitation signal. For continuous lead-off detection, an out-of-band AC current can be applied externally to the input and digitally processed to determine electrode impedance.

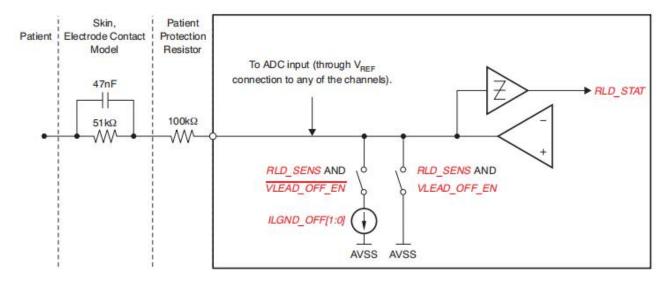

#### 9.3.12 Bias Drive (BIAS) Lead-off Detection

During normal operation of the CBM24AD98Q, right leg drive (RLD) lead-off detection cannot be utilized since the detection requires the disabling of the right leg drive amplifier. As depicted in Figure 9.3.14, the CBM24AD98Q employs a current source and a comparator to ascertain the connection state of the BIAS electrode. When the BIAS amplifier is powered on, the current source is inactive. The acceptable threshold for BIAS impedance can be determined by setting the reference level of the comparator, which is set in a manner identical to the threshold setting for other negative input signals, using the LOFF[7:5] bits. This threshold setting allows for the determination of the BIAS electrode's connectivity status.

Figure 9.3.14. RLD Lead-Off Detection at Power Up

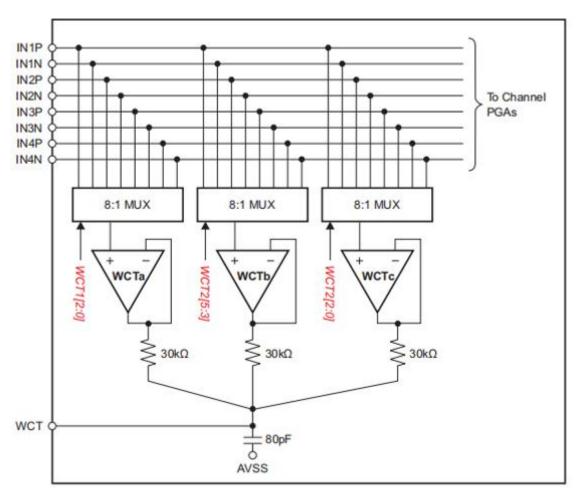

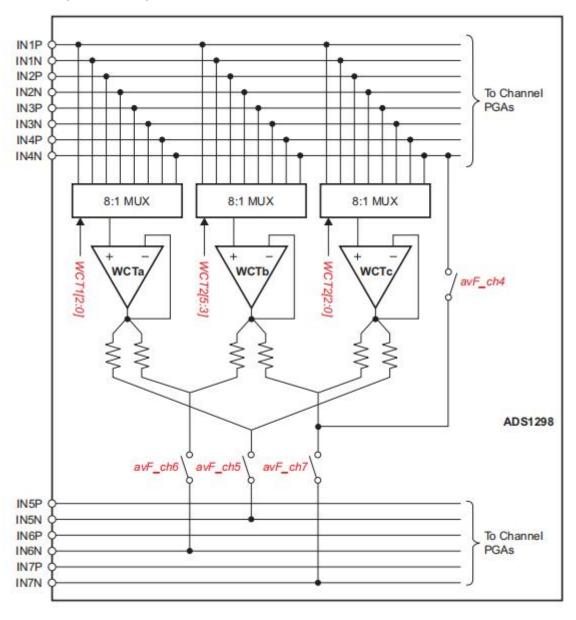

### Wilson Central Terminal (WCT) and Augmented Leads

In a standard 12-lead ECG, the WCT voltage is defined as the average potential of the right arm (RA), left arm (LA), and left leg (LL) electrodes. This voltage serves as the reference voltage for measurements of the precordial leads. Integrated within the CBM24AD98Q chip are three low-noise amplifiers capable of generating the WCT voltage, as illustrated in Figure 9.3.15. Any one of the eight signals (from IN1P through IN4N) can be routed to each of these amplifiers to compute the average. This versatility enables the RA, LA, and LL electrodes to be connected to any input of the first four channels, depending on the lead configuration adopted. The adaptive design accommodates various lead setups while maintaining the essential function of the WCT as a stable reference point for electrocardiographic readings.

Figure 9.3.15 WCT lead generation circuit

Each of the three amplifiers in the WCT circuit can be individually powered down via register settings. By powering two amplifiers, the average potential of any two electrodes can be generated at the WCT pin. Notably, the drive strength of the WCT amplifiers is limited; thus, if they are utilized to drive low-impedance loads, buffering is advisable. Upon powering multiple WCT amplifiers, the overall noise level decreases, as depicted in Table 9.3.3. This noise reduction phenomenon arises from the averaging effect achieved by the passive summation network at the amplifier outputs. Power savings from disabling buffers are negligible, primarily due to a significant portion of the circuitry being shared among the three amplifiers. The bandwidth of the WCT node is constrained by an RC network. Internally, the summation network consists of three  $30k\Omega$  resistors and an 80pF capacitor. For optimal performance, an external 100pF capacitor is recommended to be added. The effective bandwidth is dependent on the number of amplifiers that are active. The WCT node can drive extremely high input impedances, typically exceeding  $500M\,\Omega$ . A common application involves connecting this WCT signal to the negative input terminal of the CBM24AD98Q, serving as the reference signal for precordial leads.

### Table 9.3.3: Typical WCT Performance with 1, 2, or 3 Buffers Enabled.

This table outlines the variations in WCT performance characteristics when employing one, two, or all three of the available buffers, highlighting key metrics such as noise level, power consumption, and effective bandwidth under different operational configurations.

| PARAMETER       | ANY ONE<br>(A, B, or C) | ANY TWO<br>(A+B, A+C, or B+C) | ALL THREE<br>(A+B+C) | UNIT              |

|-----------------|-------------------------|-------------------------------|----------------------|-------------------|

| ntegrated noise | 540                     | 382                           | 312                  | nV <sub>RMS</sub> |

| Power           | 53                      | 59                            | 65                   | μW                |

| -3-dB BW        | 30                      | 59                            | 89                   | kHz               |

| Slew rate       | BW limited              | BW limited                    | BW limited           | V/µs              |

As previously mentioned, all three WCT amplifiers can be connected to any one of the eight analog input pins. The inputs to these amplifiers are subject to chopper modulation, with the chopping frequency varying according to the data rate setting of the CBM24AD98Q. The chopping frequencies for the three highest data rates maintain a 1:1 ratio. For instance, at a data rate of 32k samples per second (32kSPS) in HR mode, the chopping frequency is 32kHz when WCT\_CHOP is set to 0. Conversely, the chopping frequencies for the four lower data rates are fixed at 4kHz. When WCT\_CHOP is set to 1, the chopping frequency is locked to the highest data rate frequency, specifically fMOD/16, as illustrated in Table 9.3.4.This out-of-band chopping does not interfere with ECG-related measurements. However, if a channel connected to a WCT amplifier, such as the V lead channel, has its output linked to a pacing signal amplifier used for detecting external pacing signals, chopper artifacts may become evident at the output of the pacing signal amplifier.

**Table 9.3.4: WCT Chopping Frequencies**

| CONFIG1.DR[2:0] BIT | CONFIG2.WCT_CHOP = 0   | CONFIG2.WCT_CHOP = 1  |  |

|---------------------|------------------------|-----------------------|--|

| 000                 | f <sub>MOD</sub> /16   | f <sub>MOD</sub> /16  |  |

| 001                 | f <sub>MOD</sub> / 32  | f <sub>MOD</sub> / 16 |  |

| 010                 | f <sub>MOD</sub> / 64  | f <sub>MOD</sub> / 16 |  |

| 011                 | f <sub>MOD</sub> / 128 | f <sub>MOD</sub> / 16 |  |

| 100                 | f <sub>MOD</sub> / 128 | f <sub>MOD</sub> / 16 |  |

| 101                 | f <sub>MOD</sub> / 128 | f <sub>MOD</sub> / 16 |  |

| 110                 | f <sub>MOD</sub> / 128 | f <sub>MOD</sub> / 16 |  |

In a typical 12-lead ECG application with eight channels, augmented leads are computed digitally. However, there may be instances where all leads, including the augmented ones, are required to be derived in an analog (as opposed to digital) form. The CBM24AD98Q offers the option to generate these augmented leads by routing the respective averages to Channels 5, 6, and 7. The same three amplifiers utilized for creating WCT signals are also employed in generating the Wilson Central Terminal (WCT) signal. Figure 9.3.16 illustrates an example of generating

augmented leads in the analog domain. More than eight channels are utilized in this depiction to produce the standard 12 leads; hence, this functionality is not available on the CBM24AD98Q-4 or CBM24AD98Q-6 variants. This highlights a scenario where additional hardware capabilities facilitate the analog derivation of all necessary ECG leads directly, bypassing the need for digital post-processing for the augmented leads.

Figure 9.3.16 Enhanced leads

## **Product Function Modes**

# Product Function Modes Start (START)

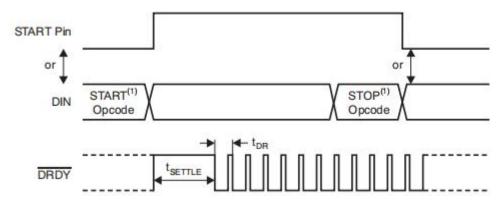

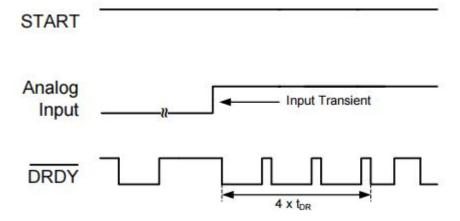

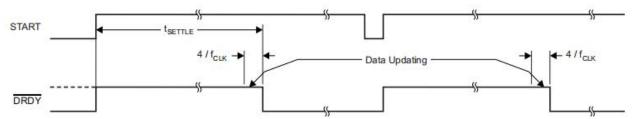

Initiating a conversion can be achieved by pulling the START pin high for at least 2 tCLK cycles, or by issuing a START command. When START is low and no START command has been transmitted, the chip does not assert the DRDY\_ signal (conversion is paused). When utilizing the START command to control conversions, maintain the START pin at a low level. The CFYA98 features two operational modes for controlling conversions: Continuous mode and Single-shot mode, which is selected by the SINGLE SHOT bit (bit 3 of the CONFIG4 register). In multi-chip configurations, the START pin serves to synchronize the chips. The settling time (tSETTLE) refers to the duration required for output data to become fully stable after the analog-to-digital conversion begins. Upon the assertion of START, DRDY is also pulled high. The subsequent falling edge of DRDY signifies that the data is ready. Figure 9.4.1 illustrates the timing diagram, while Table 9.4.1 lists the settling times for various data rates. The settling time depends on fCLK and the decimation rate (controlled by the DR[2:0] bits in the CONFIG1 register). Following the initial settling period, DRDY goes low, indicating that the data conversion is complete and will appear at the set data rate tDR. If data is not read back from DOUT before the next conversion is ready, DRDY goes high for 4 tCLK periods before returning low, signaling new data readiness. Note that when START remains high and there is a step change in the input signal, the filter requires 3×tDR to stabilize to the new value. Stable data is then ready at the fourth DRDY falling edge.

Figure 9.4.1 Stability time

Table 9.4.1 Establishment time for different data rates

| DR[2:0] | Normal mode | Unit             |  |

|---------|-------------|------------------|--|

| 000     | 521         | t <sub>CLK</sub> |  |

| 001     | 1033        | t <sub>CLK</sub> |  |

| 010 | 2057  | t <sub>CLK</sub> |

|-----|-------|------------------|

| 011 | 4105  | t <sub>CLK</sub> |

| 100 | 8201  | t <sub>CLK</sub> |

| 101 | 16393 | t <sub>CLK</sub> |

| 110 | 32777 | t <sub>CLK</sub> |

## Reset (RESET )

There are two methods to reset the CBM24AD98Q: by pulling the RESET\_ pin low or by sending a RESET command. When using the RESET\_ pin, ensure compliance with the minimum pulse duration timing specification before pulling the pin back high. The RESET command takes effect on the eighth falling edge of SCLK after the command is issued. Following a reset, 18 tCLK cycles are required to initialize configuration registers to their default states and commence the conversion cycle. Note that an internal reset to the digital filter is automatically issued when the CONFIG1 register is set to a new value using the WREG command.9.4.3 Power-Down (PWDN\_) All on-chip circuits are shut off when the PWDN\_ pin is pulled low. To exit power-down mode, the PWDN\_ pin should be pulled high. After exiting power-down mode, the internal oscillator and reference require time to wake up. It is recommended to disable the external clock during power-down to conserve power.

#### **Data Acquisition**

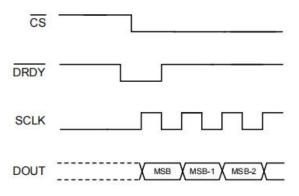

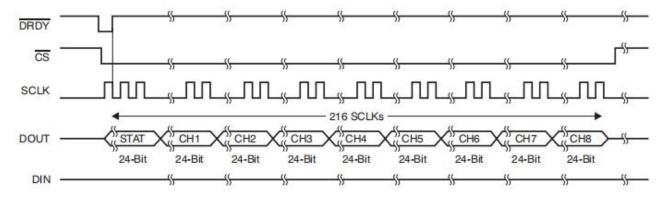

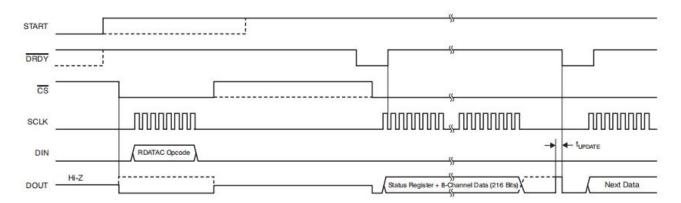

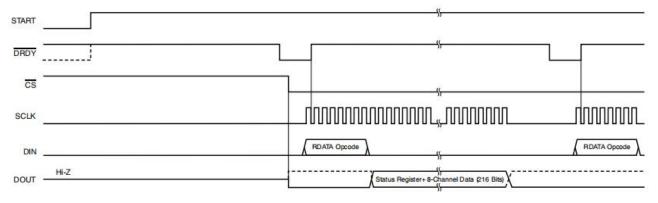

#### (1) Data Ready (DRDY)

DRDY\_ is an output signal that transitions from high to low to indicate new conversion data is ready. The CS\_ signal has no effect on the data ready signal. The behavior of DRDY\_ depends on whether the chip is in RDATAC mode, continuously outputting data, or using RDATA commands for on-demand data reads. When reading data with the RDATA command, the read operation can overlap with the next DRDY\_ without data corruption. The START pin or START command places the chip into either normal data capture mode or pulsed data capture mode. Figure 9.4.2 illustrates the relationship between DRDY\_, DOUT, and SCLK during data read operations. DOUT is latched on the rising edge of SCLK, and DRDY\_ is pulled high on the falling edge of SCLK. Note that DRDY\_ goes high on the first falling edge of SCLK, regardless of whether data is being read or commands are being sent via the DIN pin.

Figure 9.4.2 DRDY\_ with data retrieval (CS=0)

#### (2) Data Readout

Data readout can be accomplished through one of the following two methods:

- 1. RDATAC: The Continuous Data Read Command sets the chip into continuous read mode, where new data is automatically loaded into the output shift register upon completion of each data conversion without the need to send a command. For more detailed information, refer to the RDATAC: Continuous Data Read section.

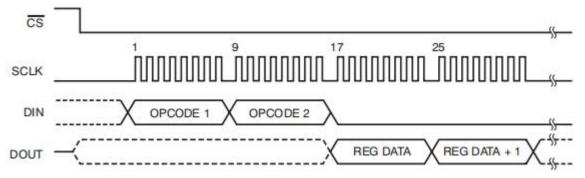

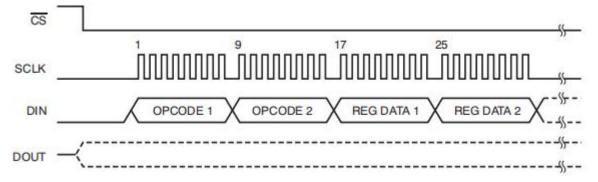

- 2. RDATA: The Data Read Command requires sending a command to the chip to load the latest data into the output shift register. For more detailed information, see the RDATA: Data Read section.Conversion data is read out by shifting data out on DOUT. The MSB of the data on DOUT is output on the first rising edge of SCLK. DRDY\_returns high on the first falling edge of SCLK for the entire read operation. DIN should remain low for the duration of the read operation. The number of bits in the data output depends on the number of channels and the number of bits per channel. For an 8-channel CBM24AD98Q, the amount of data output is [24 status bits + (24 bits x 8 channels) = 216 bits]. The format of the 24 status bits is: (1100 + LOFF\_STATP + LOFF\_STATN + bits [4:7] of the GPIO register). The data format for each channel is a two's complement binary format with the MSB first. When channels are turned off using user register settings, the corresponding channel output is set to "0". However, the order of channel outputs remains unchanged. The CBM24AD98Q also offers multireadback functionality. By simply providing more SCLKs in RDATAC mode, data can be read multiple times, in which case the MSB data byte repeats after reading the last byte. For multireadback, the DAISY\_EN\_ bit in the CONFIG1 register must be set to "1".

#### 9.4.5 Continuous Conversion Mode

Conversions begin when the START pin is pulled high or a START command is sent. As shown in Section 9.4.3, the DRDY\_ output goes high when the conversion starts and goes low when the

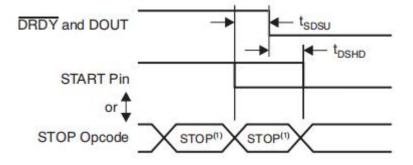

data is ready. Conversions will continue indefinitely until the START pin goes low or a STOP command is sent. When the START pin is pulled low or a STOP command is issued, the currently ongoing conversion is allowed to complete. Figures 9.4.4 and Table 9.4.2 depict the timing of the START pin or the START and STOP commands to the DRDY\_ signal during data conversion. tSDSU indicates when the START pin should be pulled low or when the STOP command should be sent before the falling edge of DRDY\_ to halt further conversions. tDSHD indicates when the START pin should be pulled low or when the STOP command should be sent after the falling edge of DRDY\_ to complete the current conversion and halt further conversions. To keep the converter running continuously, the START pin can be kept high. When switching from Single-Shot mode to continuous conversion mode, pull the START signal low then high again, or send a STOP command followed by a START command. This conversion mode is suitable for applications requiring a fixed, continuous stream of conversions.

\*\*The START and STOP commands take effect on the 7th falling edge of SCLK.

Figure 9.4.3 Continuous Conversion Mode

The START and STOP commands take effect on the seventh falling edge of the SCLK at the end of the command.

Figure 9.4.4 Start to DRDY timing

**Table 9.4.2 Time series characteristics**

|                   |                                                                             | MIN | MAX | UNIT             |

|-------------------|-----------------------------------------------------------------------------|-----|-----|------------------|

| t <sub>SDSU</sub> | START pin low or STOP opcode to DRDY setup time to halt further conversions | 16  |     | t <sub>CLK</sub> |

| t <sub>DSHD</sub> | START pin low or STOP opcode to complete current conversion                 | 16  |     | tCLK             |

## 9.4.6 Single-Shot Mode

Single-shot mode is enabled by setting the SINGLE\_SHOT bit in the CONFIG4 register to "1". In single-shot mode, the CBM24AD98Q performs a single conversion when the START pin is pulled high or a START command is issued. As illustrated in Figure 9.4.5, upon completion of the conversion, DRDY\_ goes low and halts further conversions. DRDY\_ remains low regardless of whether the conversion data is read or not. To initiate a new conversion, the START pin must be pulled low and then high again, or the START command must be resent. When transitioning from continuous conversion mode to single-shot mode, the START signal should be pulled low and then high again, or a STOP command should be issued before sending another START command.

Figure 9.4.5 DRDY\_ No Data Recovery in SingLE-SHOT Mode