## 产品特性

- 电源：1.8V 和 3.3V

- 内部系统时钟：1GSPS (高达 400MHz 模拟输出)

- 内置 1GSPS14 位 DAC

- 输入数据率：250MSPS

- 输出相位噪声： $\leq -124\text{dBc/Hz}$  (1kHz 偏移, 400MHz 载波)

- 窄带 SFDR：>80dB

- 8 个可编程 profile 寄存器，支持移位键控反 sinc 校正滤波器

- 参考时钟倍频功能

- 内部振荡器，支持单晶体操作

- 软件/硬件控制的省电功能

- 集成 RAM

- 调相功能

- 多芯片同步

- 与 BlackfinSPORT 轻松接口

- 4 至 252 倍可配置插值因子

- 增益控制 DAC

- 内部分频器支持高达 2GHz 的参考频率

- 封装：TQFP-100

## 产品应用

- HFC 数据、电话和视频调制解调器

- 无线基站传输

- 宽带通信传输

- 网络电话

## 产品描述

CBM99D57 可在多种高端通信系统中实现 I/Q 调制器和上变频器功能。CBM99D57 内部集成了高速直接数字频率合成器(DDS)、高速 14 位数模转换器(DAC)、时钟倍频电路、数字滤波器和其他的 DSP 功能。该芯片可在有线或无线通信系统中为数据传输提供基带上变频，并在速度、功耗和频谱性能等方面提供出色的性能。芯片支持 16 位串行输入的 I/Q 基带数据，可通过编程设置为单频正弦波信号源或插值 DAC 模式。芯片可通过内部振荡器、高速二分频电路和低噪声锁相环(PLL)来实现高速内部采样时钟。

## 目 录

|                  |    |

|------------------|----|

| 产品特性.....        | 1  |

| 产品应用.....        | 1  |

| 产品描述.....        | 1  |

| 目录.....          | 2  |

| 修订日志.....        | 3  |

| 功能框图.....        | 4  |

| 技术规格.....        | 5  |

| 引脚配置与功能描述.....   | 9  |

| 引脚简述.....        | 10 |

| 典型工作特性.....      | 12 |

| 串行 I/O 时序图.....  | 18 |

| 寄存器映射与位功能描述..... | 19 |

| 封装外形及尺寸.....     | 36 |

| 包装/订购信息.....     | 37 |

CBM99D57BQ

操作手册

## 修订日志

| 版本   | 修订日期      | 变更内容         | 变更原因 | 制作 | 审核  | 备注 |

|------|-----------|--------------|------|----|-----|----|

| V1.0 | 2026.1.21 | 更新产品工作温度错误信息 | 错误更新 | WW | LYL |    |

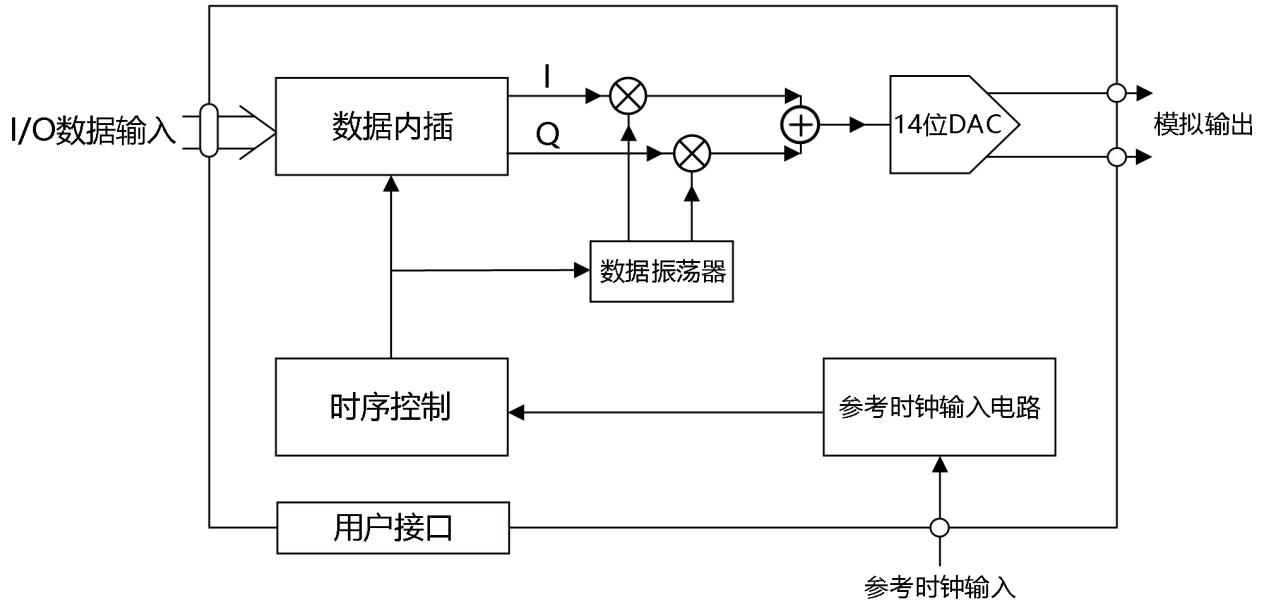

## 功能框图

图 1 CBM99D57 功能框图

## 技术规格

除非另有说明， $A_{VDD}(1.8V)$  和  $D_{VDD}(1.8V)=1.8V\pm5\%$ ， $A_{VDD}(3.3V)=3.3V\pm5\%$ ， $D_{VDD\_I/O}(3.3V)=3.3V\pm5\%$ ， $T=25^{\circ}C$ ， $RSET=10k\Omega$ ， $I_{OUT}=20mA$ ，外部参考时钟频率=1000MHz且禁用REFCLK乘法器。

| 参数                         | 测试条件/注释        | 最小值  | 典型值  | 最大值  | 单位     |

|----------------------------|----------------|------|------|------|--------|

| <b>REF_CLK 输入特性</b>        |                |      |      |      |        |

| <b>频率范围</b>                |                |      |      |      |        |

| REFCLK 乘法器                 | 禁用             | 60   |      | 1000 | MHz    |

|                            | 使能             | 3.2  |      | 60   | MHz    |

| 最大 REFCLK 输入分频器频率          | 全温度范围          | 1500 | 1900 |      | MHz    |

| 最小 REFCLK 输入分频器频率          | 全温度范围          |      | 25   | 35   | MHz    |

| 外部晶体                       |                |      | 25   |      | MHz    |

| 输入电容                       |                |      | 3.2  |      | pF     |

| 输入阻抗 (差分)                  |                |      | 2.9  |      | kΩ     |

| 输入阻抗 (单端)                  |                |      | 1.45 |      | kΩ     |

| 占空比                        | REFCLK 乘法器禁用   | 45   |      | 55   | %      |

|                            | REFCLK 乘法器使能   | 40   |      | 60   | %      |

| REF_CLK 输入电平               | 单端             | 50   |      | 1000 | mV p-p |

|                            | 差分             | 100  |      | 2000 | mV p-p |

| <b>REFCLK 乘法器 VCO 增益特性</b> |                |      |      |      |        |

| $V_{CO}$ 增益(KV) (中心频率)     | $V_{CO0}$ 范围设置 |      | 432  |      | MHz/V  |

|                            | $V_{CO1}$ 范围设置 |      | 505  |      | MHz/V  |

|                            | $V_{CO2}$ 范围设置 |      | 560  |      | MHz/V  |

|                            | $V_{CO3}$ 范围设置 |      | 754  |      | MHz/V  |

|                            | $V_{CO4}$ 范围设置 |      | 785  |      | MHz/V  |

|                            | $V_{CO5}$ 范围设置 |      | 853  |      | MHz/V  |

| <b>REFCLK_OUT 特性</b>       |                |      |      |      |        |

| 最大容性负载                     |                |      | 20   |      | pF     |

| 最大频率                       |                |      | 25   |      | MHz    |

| <b>DAC 输出特性</b>            |                |      |      |      |        |

| 满量程输出电流                    |                | 8.5  | 20   | 31.5 | mA     |

|                            |                                       |      |      |     |        |

|----------------------------|---------------------------------------|------|------|-----|--------|

| 增益误差                       |                                       | -10  |      | +10 | %FS    |

| 输出偏移                       |                                       |      |      | 3.4 | uA     |

| 微分非线性                      |                                       |      | 0.9  |     | LSB    |

| 积分非线性                      |                                       |      | 1.7  |     | LSB    |

| 输出电容                       |                                       |      | 4.5  |     | pF     |

| 残余相位噪声                     | 偏移为1kHz且 $A_{OUT}$ 为20MHz 时           |      |      |     |        |

| REFCLK 乘法器                 | 禁用                                    |      | -150 |     | dBc/Hz |

|                            | 使能, 20 倍                              |      | -141 |     | dBc/Hz |

|                            | 使能, 100 倍                             |      | -139 |     | dBc/Hz |

| 交流输出电压范围                   |                                       | -0.5 |      | 0.5 | V      |

| <b>无杂散动态范围 (SFDR 单频调制)</b> |                                       |      |      |     |        |

| $f_{OUT} = 20.1$ MHz       |                                       |      | -69  |     | dBc    |

| $f_{OUT} = 98.6$ MHz       |                                       |      | -68  |     | dBc    |

| $f_{OUT} = 201.1$ MHz      |                                       |      | -64  |     | dBc    |

| $f_{OUT} = 397.8$ MHz      |                                       |      | -55  |     | dBc    |

| <b>噪声谱密度(NSD)</b>          |                                       |      |      |     |        |

| 单频调制                       |                                       |      |      |     |        |

| $f_{OUT} = 20.1$ MHz       |                                       |      | -166 |     | dBm/Hz |

| $f_{OUT} = 98.6$ MHz       |                                       |      | -160 |     | dBm/Hz |

| $f_{OUT} = 201.1$ MHz      |                                       |      | -155 |     | dBm/Hz |

| $f_{OUT} = 397.8$ MHz      |                                       |      | -150 |     | dBm/Hz |

| 双音交调失真(IMD)                | I/Q速率= 62.2MSPS; 16倍插值                |      |      |     |        |

| $f_{OUT} = 25$ MHz         |                                       |      | -81  |     | dBc    |

| $f_{OUT} = 50$ MHz         |                                       |      | -76  |     | dBc    |

| $f_{OUT} = 100$ MHz        |                                       |      | -71  |     | dBc    |

| <b>调制器特性</b>               |                                       |      |      |     |        |

| 输入数据                       |                                       |      |      |     |        |

| 误差矢量幅度                     | 2.5Msymbols/sQPSK,4倍过采样               |      | 0.58 |     | %      |

|                            | 270.8333 ksymbols/s, GMSK, 32<br>倍过采样 |      | 0.79 |     | %      |

|                            | 2.5 Msymbols/s, 256-QAM, 4 倍<br>过采样   |      | 0.38 |     | %      |

| WCDMA-FDD(TM1), 3.84MH带宽和5MHz通道间隔            |              |      |     |  |             |

|----------------------------------------------|--------------|------|-----|--|-------------|

| 邻道泄漏比(ACLR)                                  | IF=143.88MHz |      | -76 |  | dBc         |

| 载波馈通                                         |              |      | -77 |  | dBc         |

| <b>串行端口时序特性</b>                              |              |      |     |  |             |

| 最大 SCLK 频率                                   |              | 70   |     |  | Mbps        |

| 最小 SCLK 脉冲宽度                                 | 低            | 4.5  |     |  | ns          |

|                                              | 高            | 4.5  |     |  | ns          |

| SCLK 最大上升/下降时间                               |              | 2.2  |     |  | ns          |

| 至 SCLK 最短数据建立时间                              |              | 6    |     |  | ns          |

| 至 SCLK 最短数据保持时间                              |              | 0    |     |  | ns          |

| 读取模式下最长数据有效时间                                |              |      | 11  |  | ns          |

| <b>I/O_UPDATE/PROFILE&lt;2:0&gt;/RT 时序特性</b> |              |      |     |  |             |

| 最短脉冲宽度                                       | 高            | 1    |     |  | SYNC_CLK 周期 |

| 至 SYNC_CLK 最短建立时间                            |              | 1.78 |     |  | ns          |

| 至 SYNC_CLK 最短保持时间                            |              | 0    |     |  | ns          |

| <b>I/Q 输入时序特性</b>                            |              |      |     |  |             |

| PDCLK 最大频率                                   |              | 250  |     |  | MHz         |

| 至PDCLK最短I/Q数据建立时间                            |              | 1.7  |     |  | ns          |

| 至PDCLK最短I/Q数据保持时间                            |              | 0    |     |  | ns          |

| 至PDCLK最短TxEnable 建立时间                        |              | 1.7  |     |  | ns          |

| 至PDCLK最短TxEnable 保持时间                        |              | 0    |     |  | ns          |

| <b>其它时序特性</b>                                |              |      |     |  |             |

| 唤醒时间                                         |              |      |     |  |             |

| 快速恢复模式                                       |              | 8    |     |  | SYSCLK 周期   |

| 深度睡眠模式                                       |              |      | 153 |  | us          |

| 最短复位脉冲宽度 (高电平)                               |              | 5    |     |  | SYSCLK 周期   |

| <b>数据延迟 (流水线延迟)</b>                          |              |      |     |  |             |

| 单频或 Profile 模式数据延迟                           |              |      |     |  |             |

| 频率、相位和幅度至DAC输出                               | 匹配延迟使能       |      | 91  |  | SYSCLK 周期   |

| 频率和相位至DAC输出                                  | 匹配延迟禁用       |      | 79  |  | SYSCLK 周期   |

| <b>CMOS 逻辑输入</b>                             |              |      |     |  |             |

| 电压                   |         |      |      |     |    |

|----------------------|---------|------|------|-----|----|

| 逻辑 1                 |         | 2.0  |      |     | V  |

| 逻辑 0                 |         |      |      | 0.8 | V  |

| 电流                   |         |      |      |     |    |

| 逻辑 1                 |         |      | 93   | 123 | uA |

| 逻辑 0                 |         |      | 39   | 51  | uA |

| 输入电容                 |         |      | 2.3  |     | pF |

| XTAL_SEL 输入          |         |      |      |     |    |

| 逻辑 1 电压              |         | 1.25 |      |     | V  |

| 逻辑 0 电压              |         |      |      | 0.6 | V  |

| 输入电容                 |         |      | 2.3  |     | pF |

| CMOS 逻辑输出            | 1mA 负载  |      |      |     |    |

| 电压                   |         |      |      |     |    |

| 逻辑 1                 |         | 2.8  |      |     | V  |

| 逻辑 0                 |         |      |      | 0.4 | V  |

| 电源电流                 |         |      |      |     |    |

| DVDD_I/O (3.3V) 引脚功耗 | QDUC 模式 |      | 18   |     | mA |

| DVDD (1.8V) 引脚功耗     | QDUC 模式 |      | 615  |     | mA |

| AVDD (3.3V) 引脚功耗     | QDUC 模式 |      | 29   |     | mA |

| AVDD (1.8V) 引脚功耗     | QDUC 模式 |      | 109  |     | mA |

| 功耗                   |         |      |      |     |    |

| 单频模式                 |         |      | 810  |     | mW |

| 连续调制8倍插值             |         | 1415 | 1820 | mW  |    |

| 反Sinc滤波器功耗           |         |      | 155  | 208 | mW |

| 深度睡眠模式               |         |      | 15   | 30  | mW |

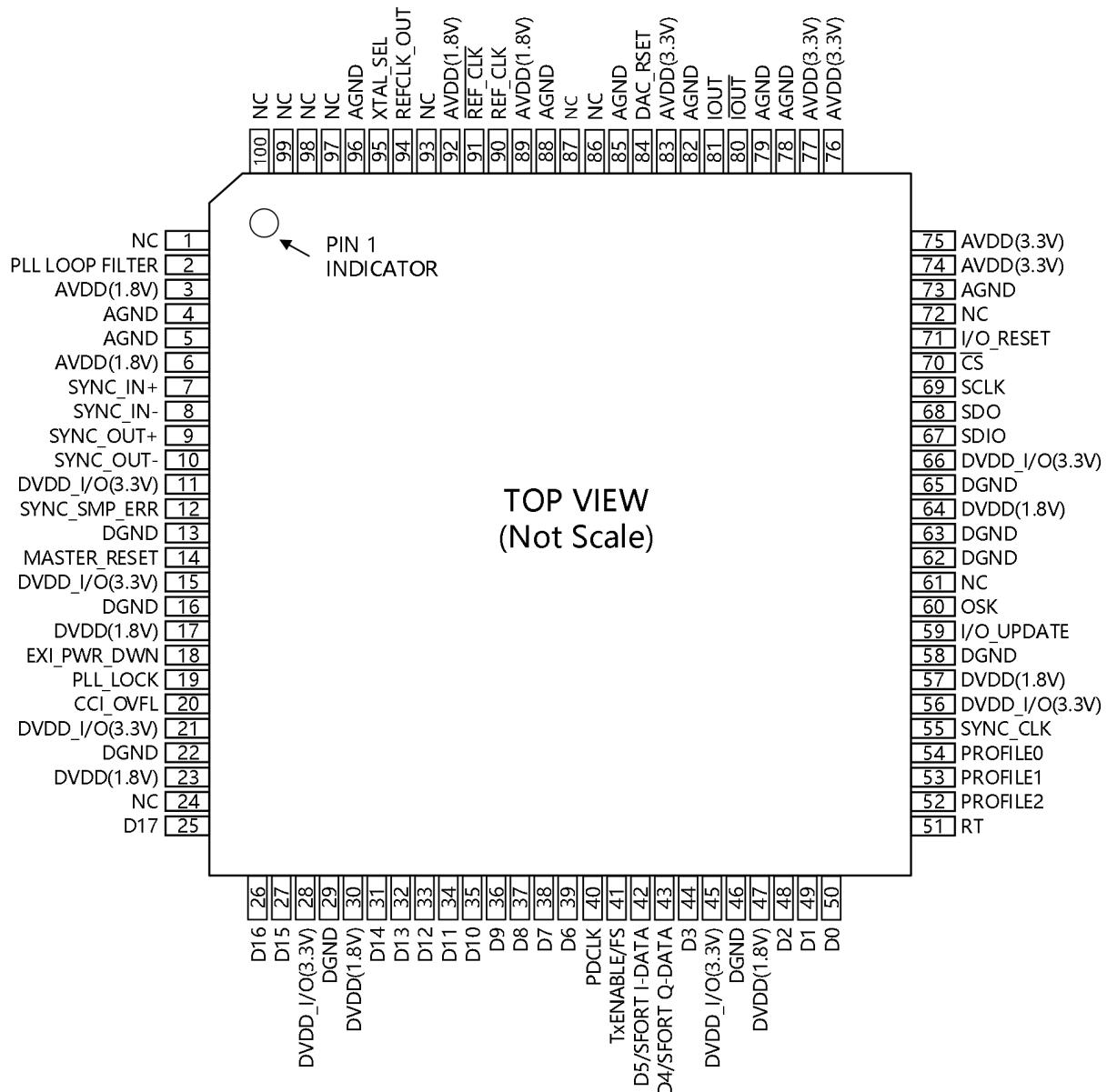

## 引脚配置与功能描述

TOP VIEW

(Not Scale)

图 2 芯片管脚图

## 引脚简述

| 引脚编号                        | 引脚名称                        | I/O | 描述                                                                                 |

|-----------------------------|-----------------------------|-----|------------------------------------------------------------------------------------|

| 1/24/61/72/86/87/93/97至100  | NC                          |     | 不连接。允许器件引脚悬空。                                                                      |

| 2                           | PLL_LOOP_FILTER             | I   | PLL 环路滤波器补偿。                                                                       |

| 3/6/89/92                   | A <sub>VDD</sub> (1.8V)     | I   | 模拟内核 VDD。1.8 V 模拟电源。                                                               |

| 74 至 77/83                  | A <sub>VDD</sub> (3.3V)     | I   | 模拟 DAC VDD。3.3 V 模拟电源。                                                             |

| 17/23/30/47/57/64           | D <sub>VDD</sub> (1.8V)     | I   | 数字内核 VDD。1.8 V 数字电源。                                                               |

| 11/15/21/28/45/56/66        | D <sub>VDD</sub> _I/O(3.3V) | I   | 数字输入/输出 VDD。3.3 V 数字电源。                                                            |

| 4/5/73/78/79/82/85/88/96    | A <sub>GND</sub>            | I   | 模拟地。                                                                               |

| 13/16/22/29/46/58/62/63/65  | D <sub>GND</sub>            | I   | 数字地。                                                                               |

| 7                           | SYNC_IN+                    | I   | 同步信号，数字输入（上升沿有效）。外部主机的同步信号同步内部子时钟。）                                                |

| 8                           | SYNC_IN-                    | I   | 同步信号，数字输入（下降沿有效）。外部主机的同步信号同步内部子时钟。）                                                |

| 9                           | SYNC_OUT+                   | O   | 同步信号，数字输出（上升沿有效）。内部器件子时钟的同步信号同步外部从机。）                                              |

| 10                          | SYNC_OUT-                   | O   | 同步信号，数字输出（下降沿有效）。内部器件子时钟的同步信号同步外部从机。                                               |

| 12                          | SYNC_SMP_ERR                | O   | 同步采样误差，数字输出（高电平有效）。此引脚高电平表明芯片未收到有效 SYNC_IN+/SYNC_IN.同步信号。                          |

| 14                          | MASTER_RESET                | I   | 主机复位，数字输入（高电平有效）。此引脚将所有存储元件清 0，寄存器设置为默认值。                                          |

| 18                          | EXT_PWR_DWN                 | I   | 外部省电模式，数字输入（高电平有效）。此引脚高电平会启用当前编程的省电运行模式。如未使用，应接地。                                  |

| 19                          | PLL_LOCK                    | O   | PLL 锁定，数字输出（高电平有效）。此引脚高电平表示时钟乘法器 PLL已锁定参考时钟输入。                                     |

| 20                          | CCI_OVFL                    | O   | CCI 溢出数字输出,高电平有效。此引脚高电平表示 CCI 滤波器溢出。此引脚会一直保持高电平状态，直到 CCI 溢出条件清除为止。                 |

| 25至27、31至39、<br>42至44、48至50 | D<17:0>                     | I/O | 并行数据输入总线（高电平有效）。这些引脚为调制器提供交错式 18 位数字 I 和 Q 矢量，以便完成上变频。还可在 Blackfin 接口模式下用作GPIO 端口。 |

| 42                          | SPORT I-DATA                | I   | 在 Blackfin 接口模式下，此引脚作为 I 路数据串行输入。                                                  |

| 43                          | SPORT Q-DATA                | I   | 在 Blackfin 接口模式下，此引脚作为 Q 路数据串行输入。                                                  |

| 40                          | PDCLK                       | O   | 并行数据时钟，数字输出（时钟）。                                                                   |

| 41                          | TxENABLE /FS                | I   | 发送使能，数字输入（高电平有效）。FS输入：在Blackfin 接口模式下，此引脚用作FS输入端，接收来自Blackfin 的RFS输出信号             |

|         |                  |     |                                                                                                                                          |

|---------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

| 51      | RT               | I   | RAM 触发器, 数字输入 (高电平有效)。此引脚为 RAM 幅度调整功能提供控制。使用此功能时, 高电平从起始 RAM 地址到结尾地址扫描幅度。低电平从结尾 RAM 地址到起始地址扫描幅度。如果未使用, 应接地或连接电源。                         |

| 52 至 54 | PROFILE<2:0>     | I   | Profile 选择引脚, 数字输入 (高电平有效)。这些引脚用于选择 DDS 内核的八个相位/频率特性之一 (单音或载波音)。通过改变其中一个引脚的状态, 可将所有当前 I/O 缓冲内容传输到相应寄存器。要改变状态, 需要参考 SYNC_CLK 引脚上的信号来建立信号。 |

| 55      | SYNC_CLK         | O   | 输出系统时钟/4, 数字输出 (时钟)。I/O_UPDATE 和 PROFILE<2:0>引脚信号根据此信号来建立。                                                                               |

| 59      | I/O_UPDATE       | I/O | 输入/输出更新; 数字输入或输出 (高电平有效), 取决于内部 I/O 更新有效位。此引脚高电平表示 I/O 缓冲内容将传输到相应的内部寄存器。                                                                 |

| 60      | OSK              | I   | 输出移位键控, 数字输入 (高电平有效)。使用 OSK (手动或自动) 时, 此引脚控制 OSK 功能。未使用 OSK 时, 此引脚连到高电平。                                                                 |

| 67      | SDIO             | I/O | 串行数据输入/输出, 数字输入/输出 (高电平有效)。根据配置情况, 此引脚支持单向和双向 (默认) 两种模式。如果是双向串行端口模式, 此引脚可用于串行数据输入和输出。如果是单向模式, 仅支持数据输入。                                   |

| 68      | SDO              | O   | 串行数据输出, 数字输出 (高电平有效)。此引脚仅对单向串行数据模式有效, 用于数据输出。双向模式中, 此引脚无操作, 应悬空。                                                                         |

| 69      | SCLK             | I   | 串行数据时钟。数字时钟 (上升沿执行写操作, 下降沿执行读操作)。此引脚提供控制数据路径的串行数据时钟。芯片写操作使用上升沿, 回读操作使用下降沿。                                                               |

| 70      | CS               | I   | 片选, 数字输入 (低电平有效)。引脚低电平可使芯片检测串行时钟上升/下降沿。引脚高电平可使芯片忽略串行数据引脚输入。                                                                              |

| 71      | I/O_RESET        | I   | 输入/输出复位, 数字输入 (高电平有效)。通信周期出现故障期间变为高电平时, 此引脚并不会复位整个器件, 而是复位串行端口控制器的状态机并清空自上次 I/O 更新以来写入的任何 I/O 缓冲器。未使用时, 此引脚应接地, 以免出现意外复位。                |

| 80      | I <sub>OUT</sub> | O   | 开源 DAC 互补输出电流源。模拟输出, 电流模式。通过 50 Ω 电阻连接到 AGND。                                                                                            |

| 81      | I <sub>OUT</sub> | O   | 开源 DAC 输出电流源。模拟输出, 电流模式。通过 50 Ω 电阻连接到 AGND。                                                                                              |

| 84      | DAC_RSET         | O   | 模拟基准引脚。此引脚对 DAC 输出满量程基准电流编程。通过一个 10kΩ 电阻连接到 AGND。                                                                                        |

| 90      | REF_CLK          | I   | 参考时钟输入。模拟输入。                                                                                                                             |

| 91      | REF_CLK          | I   | 互补参考时钟输入。模拟输入。                                                                                                                           |

| 94      | REFCLK_OUT       | O   | 参考时钟输出。模拟输出。                                                                                                                             |

| 95      | XTAL_SEL         | I   | 晶体选择。                                                                                                                                    |

1. I = 输入, O = 输出。

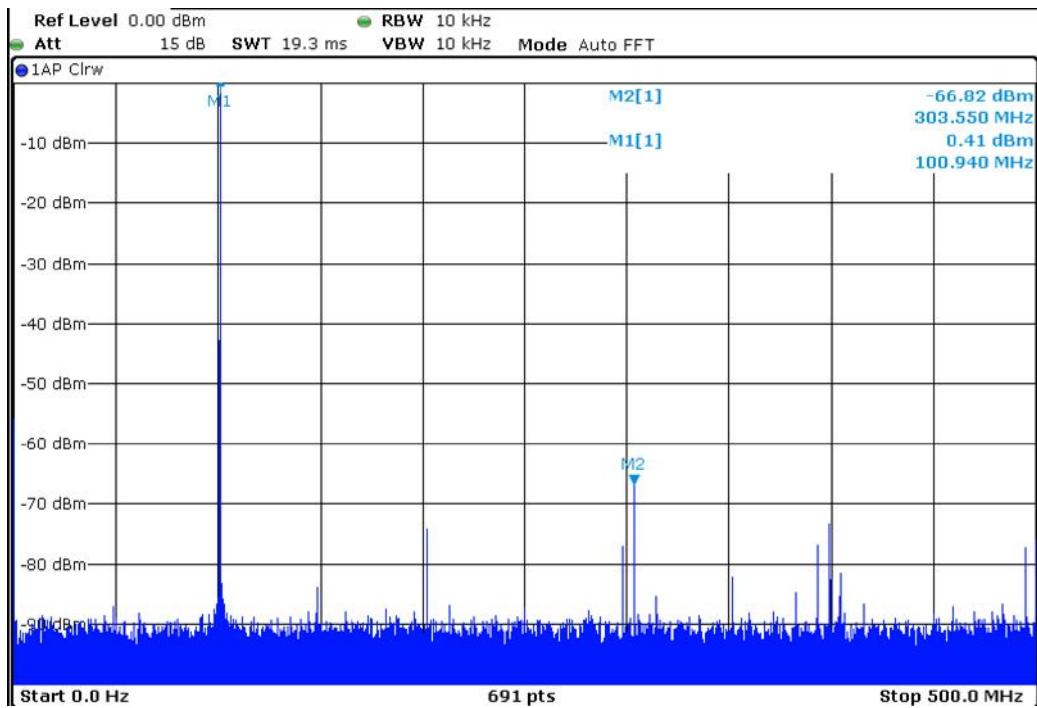

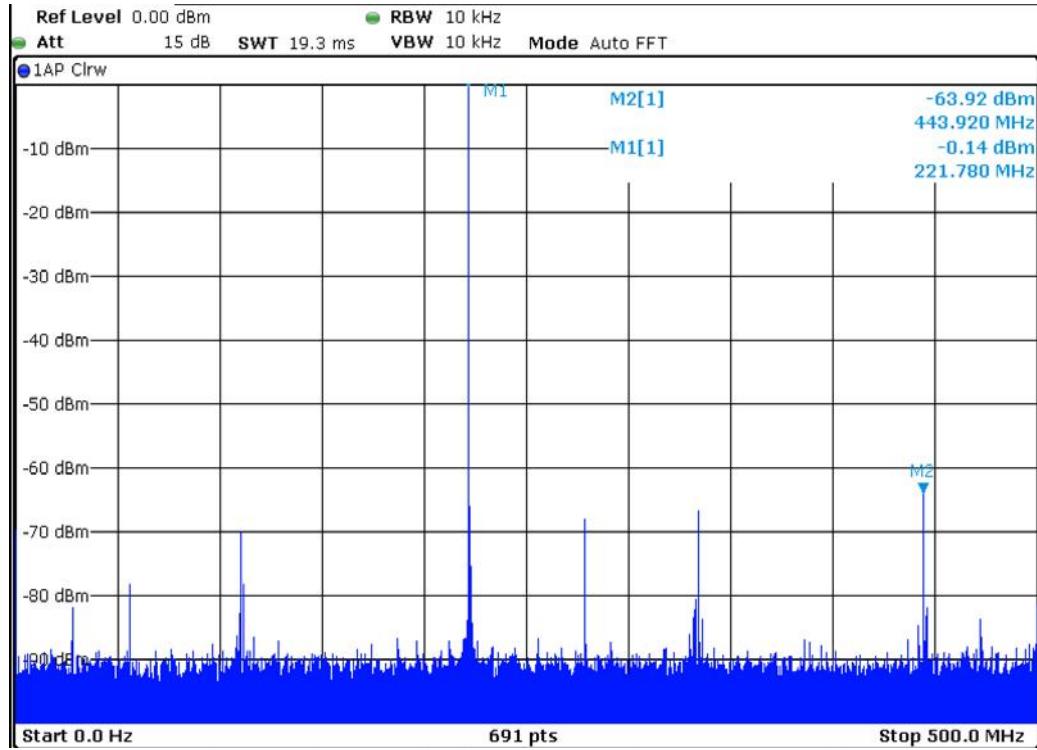

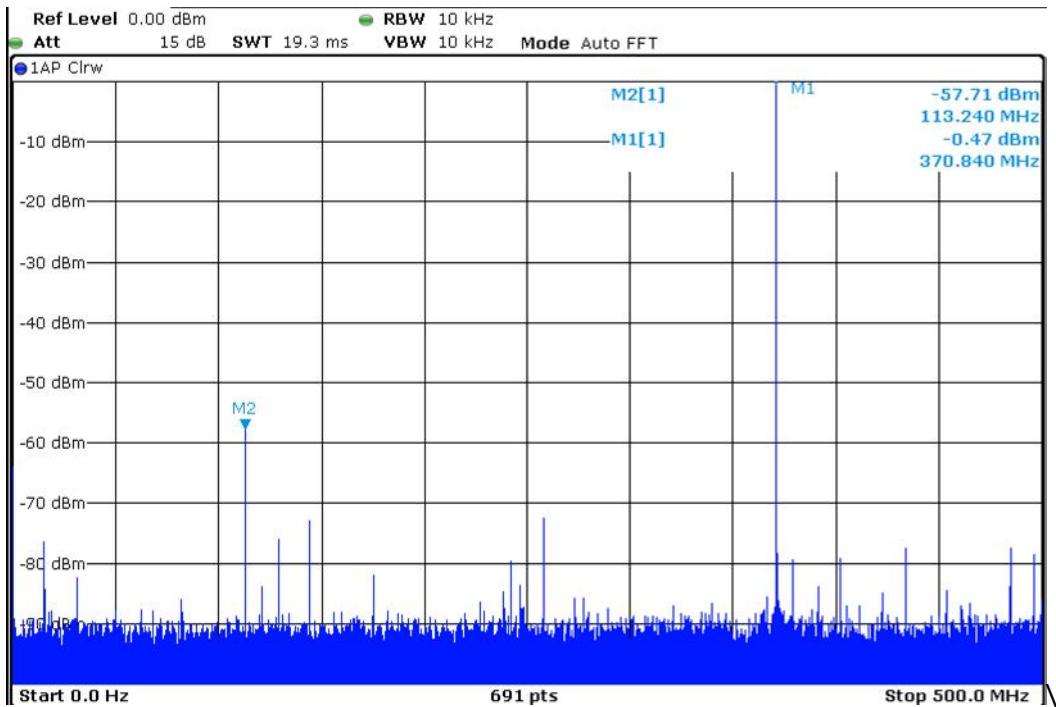

## 典型工作特性

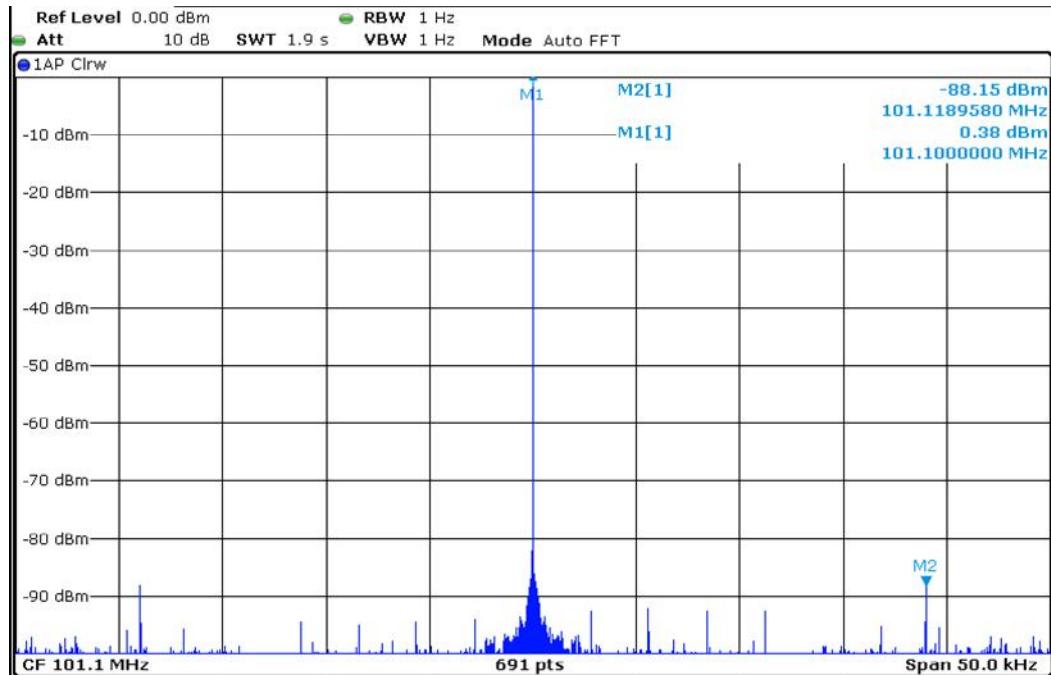

图 3 15.625KHz 正交音, 载波=101.1MHz、CCI=16 且 fs=1GHz

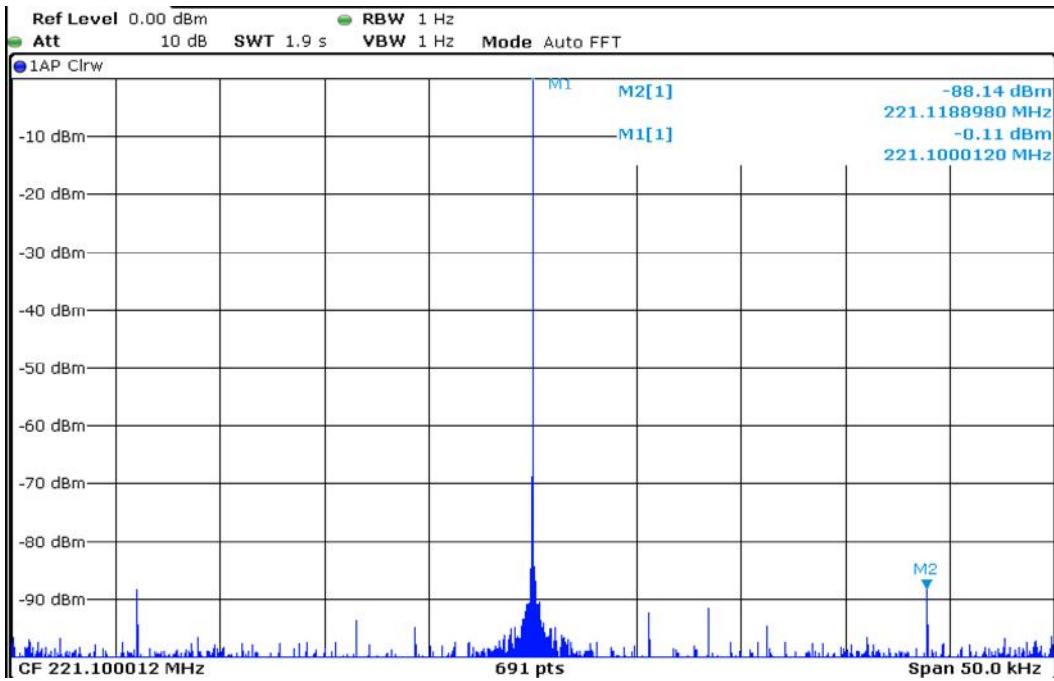

图 4 15.625 kHz 正交音, 载波 = 222.1 MHz、CCI = 16 且 fs = 1 GHz

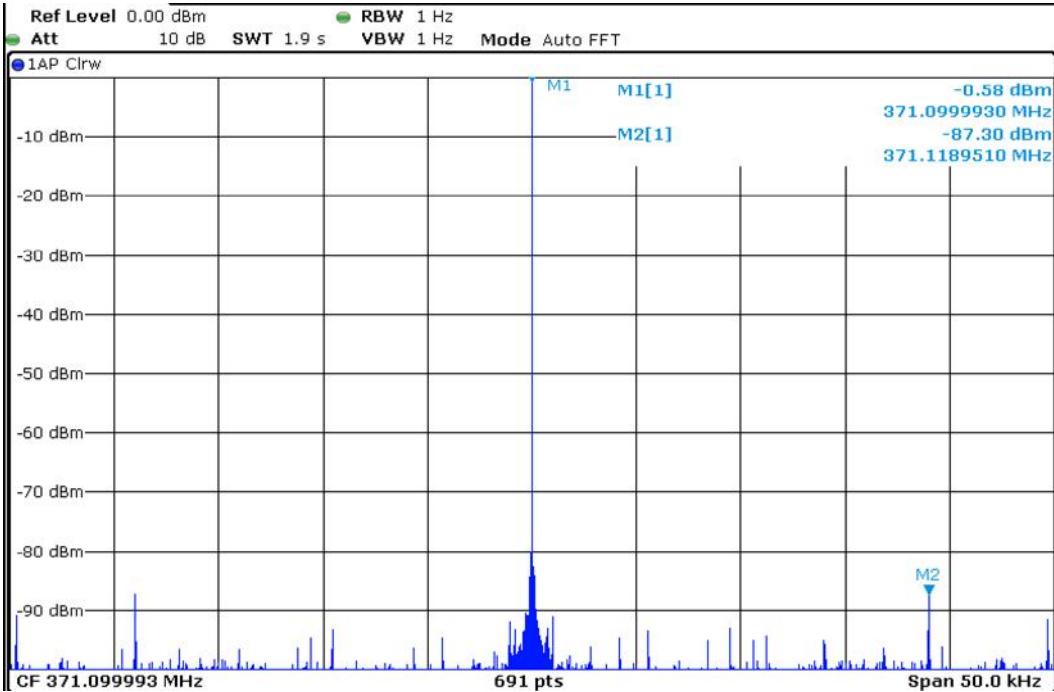

图 5 15.625 kHz 正交音，载波 = 371.1MHz、CCI = 16 且 fs = 1 GHz

图 6 图 3 的窄带视图 (带有载波和下边带抑制)

图 7 图 4 的窄带视图 (带有载波和下边带抑制)

图 8 图 5 的窄带视图 (带有载波和下边带抑制)

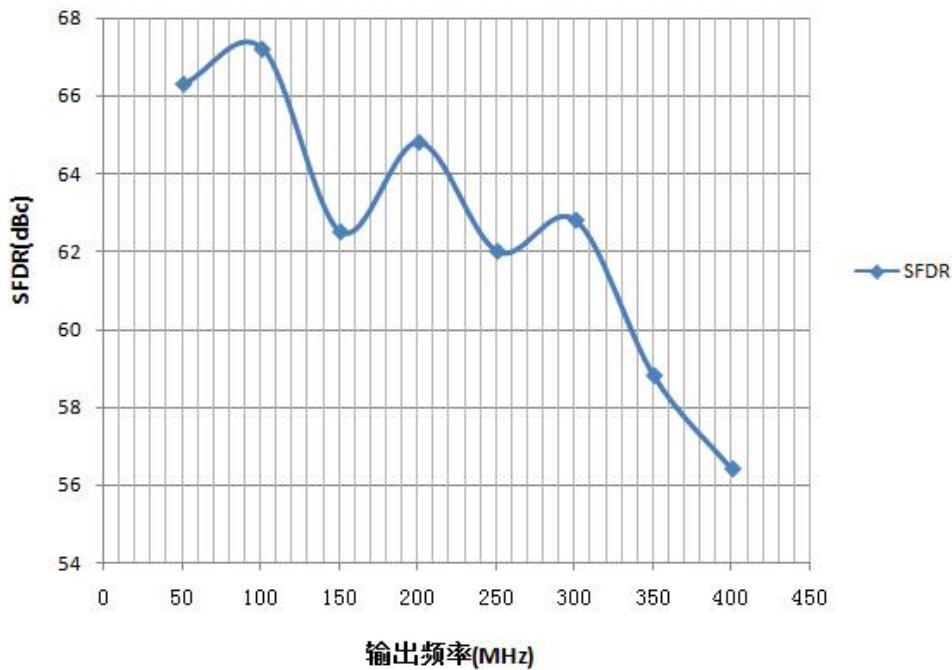

图 9 单频调制模式中宽带 SFDR 与输出频率的关系

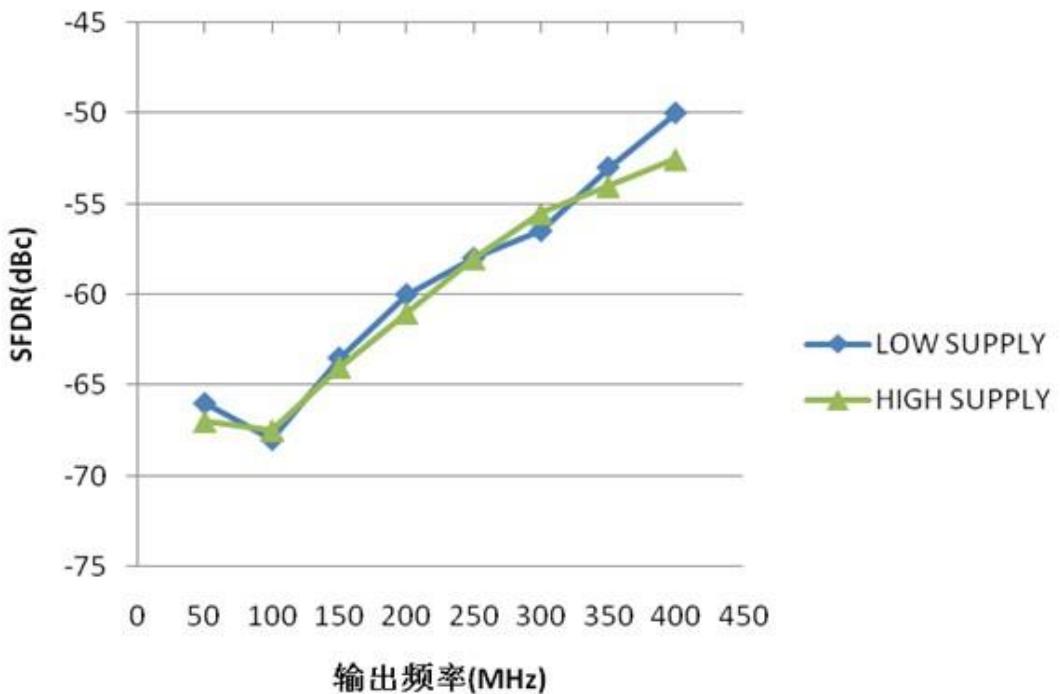

图 10 REFCLK = 1 GHz 时，单频调制模式 SFDR 输出频率和电源(±5%) 的关系

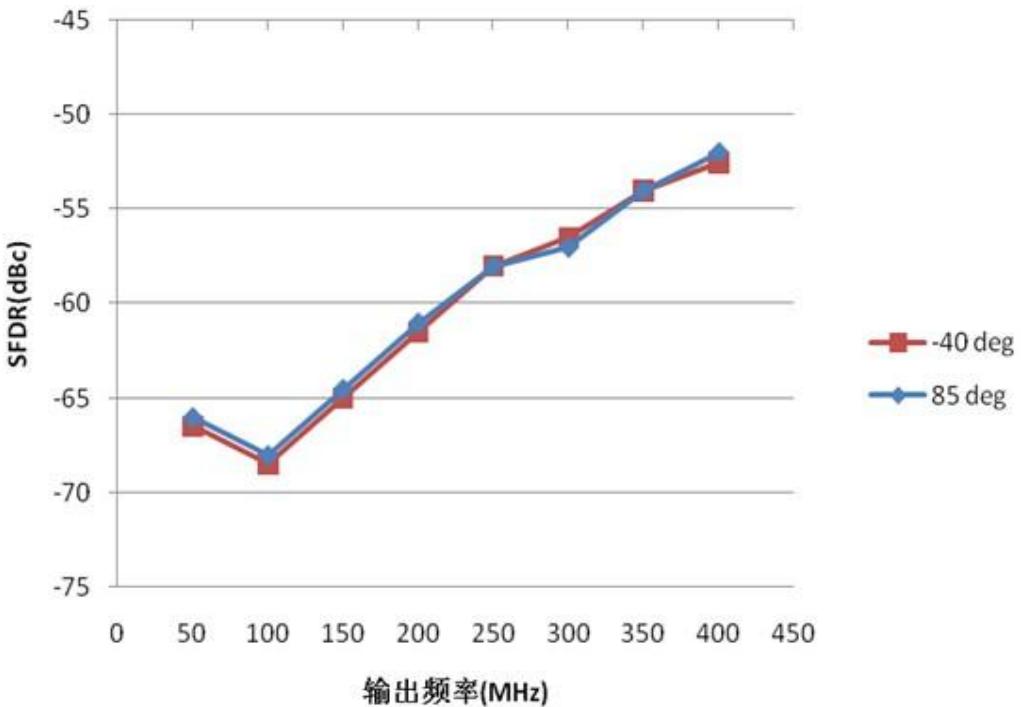

图 11 REFCLK = 1 GHz 时，单频调制模式中 SFDR 与频率和温度的关系

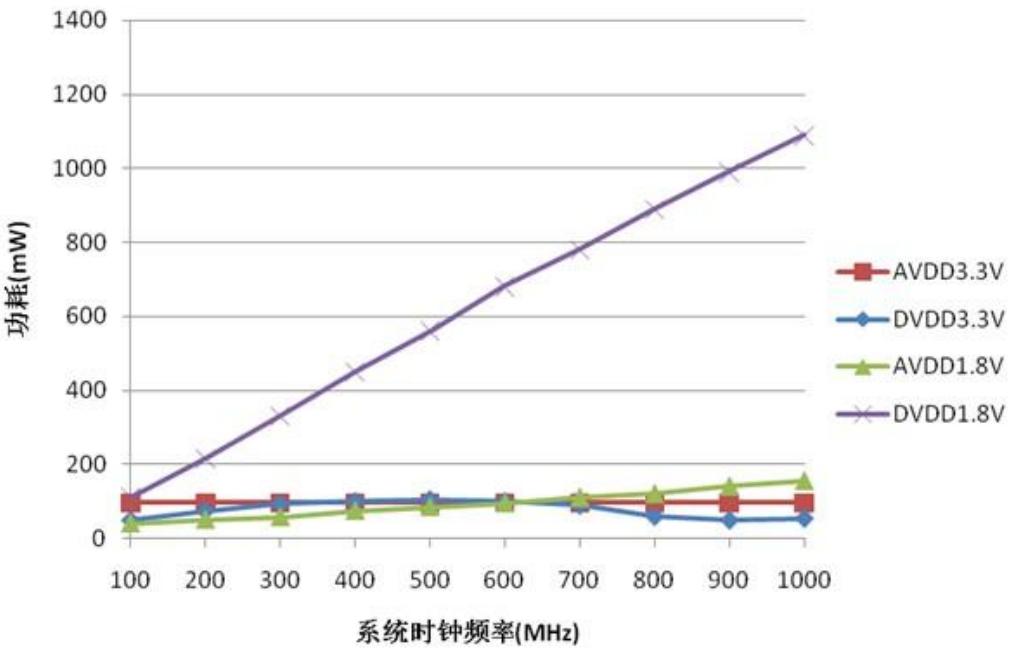

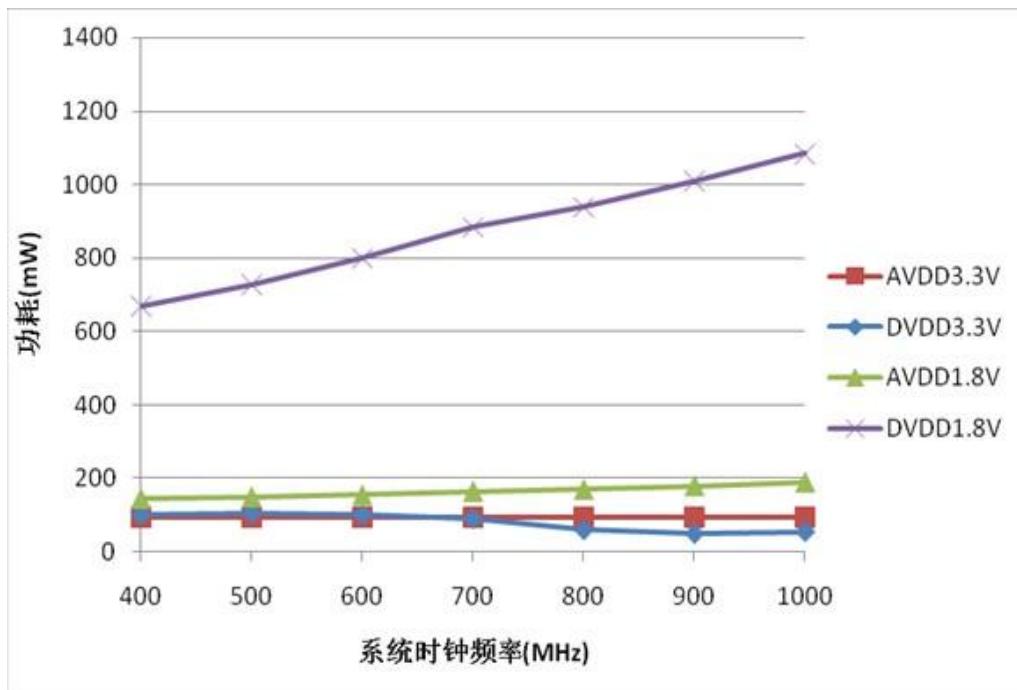

图 12 功耗与系统时钟的关系 (PLL 禁用)

图 13 功耗与系统时钟的关系 (PLL 使能)

表 1 系统时钟=1GHz 的残余相噪 (单位: dBc/Hz)

| 频偏(Hz)<br>fout(Hz) | @10  | @100 | @1k  | @10k | @100k | @1M  | @10M |

|--------------------|------|------|------|------|-------|------|------|

| 20.1M              | -135 | -145 | -155 | -161 | -167  | -167 | -167 |

| 98.6M              | -120 | -131 | -140 | -150 | -160  | -161 | -161 |

| 201.1M             | -115 | -125 | -135 | -145 | -155  | -158 | -158 |

| 397.8M             | -108 | -117 | -125 | -135 | -142  | -150 | -150 |

表 2 用 EFCLK 乘法器、REFCLK = 50 MHz × 20 且系统时钟 = 1GHz 时的残余相噪

| 频偏(Hz)<br>fout(Hz) | @10  | @100 | @1k  | @10k | @100k | @1M  | @10M |

|--------------------|------|------|------|------|-------|------|------|

| 20.1M              | -120 | -131 | -140 | -150 | -152  | -145 | -152 |

| 98.6M              | -109 | -118 | -126 | -136 | -139  | -131 | -148 |

| 201.1M             | -100 | -110 | -119 | -130 | -132  | -125 | -140 |

| 397.8M             | -91  | -101 | -110 | -120 | -123  | -115 | -131 |

## 串行 I/O 时序图

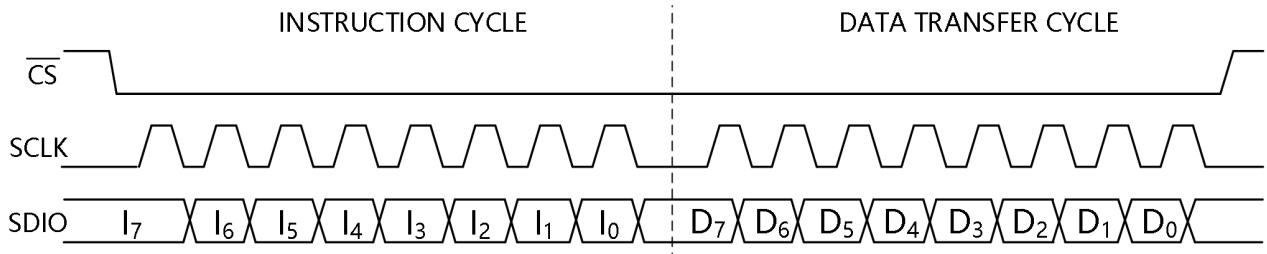

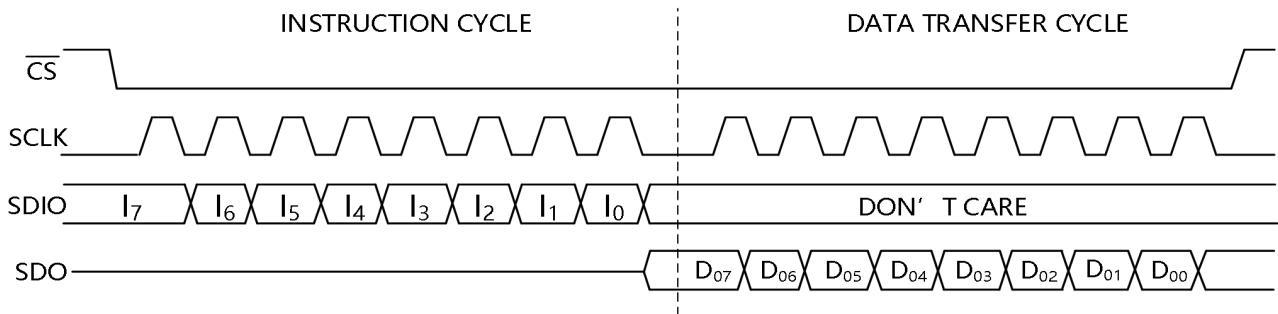

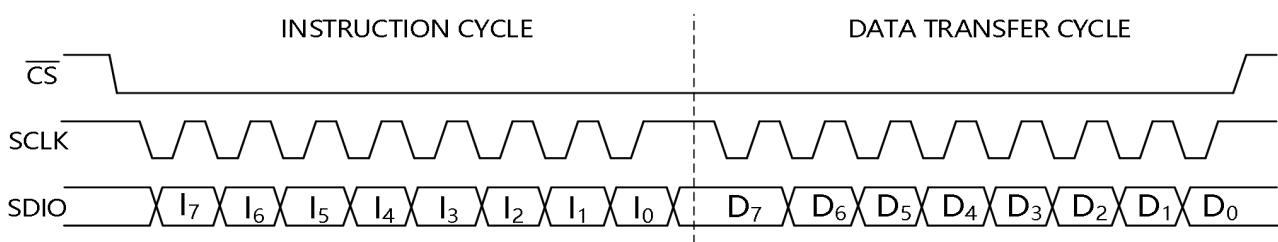

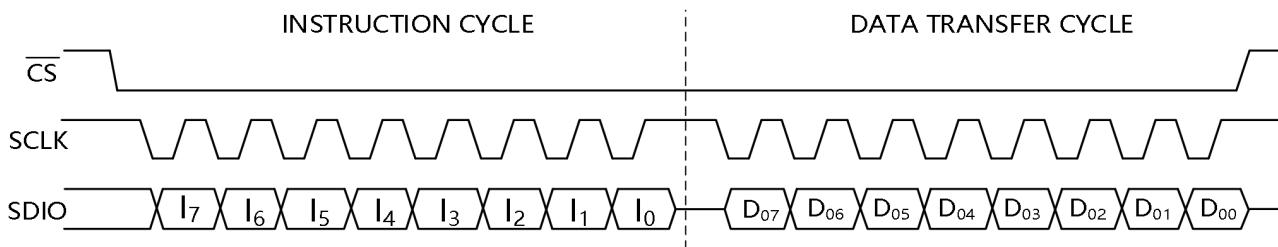

下面 4 张图给出了一些基本示例，描述串行 I/O 端口各种控制信号之间的时序关系。在 I/O 更新置位前，寄存器图中的大多数位都不会传输到其内部目的地址，这一点并未在下列时序中反映出来。

图 14 串行端口写入时序—时钟空闲为低

图 15 三线式串行端口读取时序—时钟空闲为低

图 16 串行端口写入时序—时钟空闲为高

图 17 双线式串行端口读取时序—时钟空闲为高

## 寄存器映射与位功能描述

### 寄存器映射

请注意，每个寄存器位域列中的最大数是 MSB，最小数是该寄存器的 LSB，如下表所示。

| 寄存器名称和地址                | 位地址   | 位 7(MSB)        | 位 6            | 位 5             | 位 4        | 位 3      | 位 2           | 位 1         | 位 0(LSB)              | 缺省值  |

|-------------------------|-------|-----------------|----------------|-----------------|------------|----------|---------------|-------------|-----------------------|------|

| 控制功能寄存器<br>1CFR1 (0x00) | 31:24 | RAM 使能          | 开路             |                 | RAM 回放目的位置 | 开路       |               | 工作模式        |                       | 0x00 |

|                         | 23:16 | 手动 OSK 外部控制     | 反 Sinc 滤波器使能   | CCI 清零          |            | 开路       |               |             | 选择 DDS 正弦输出           | 0x00 |

|                         | 15:8  | 开路              |                | 自动清零相位累加器       | 开路         | 清零相位累加器  | 加载 ARR@I/O 更新 | OSK 使能      | 选择自动 OSK              | 0x00 |

|                         | 7:0   | 数字部分关断          | DAC 关断         | REFCLK 输入关断     | 辅助 DAC 关断  | 外部关断控制   | 自动关断使能        | 仅为 SDIO 输入  | LSB 优先                | 0x00 |

| 控制功能寄存器<br>2CFR2 (0x01) | 31:24 | Blackfin 接口模式有效 | Blackfin 位序    | Blackfin 早帧同步使能 | 开路         |          |               |             | 将 Profile 寄存器用作 ASF 源 | 0x00 |

|                         | 23:16 | 内部 I/O 更新有效     | SYNC_CLK 使能    |                 | 开路         |          |               |             | 读取有效 FTW              | 0x40 |

|                         | 15:8  | I/O 更新速率控制      |                | PDCLK 速率控制      | 数据格式       | PDCLK 使能 | PDCLK 反转      | TXEnable 反转 | Q 优先数据配对              | 0x08 |

|                         | 7:0   | 配对延迟使能          | 数据分配器保留最后值     | 同步时序验证禁用        | 开路         |          |               |             |                       | 0x20 |

| 控制功能寄存器<br>3CFR3(0x02)  | 31:24 | 开路              |                | DRV0<1:0>       |            | 开路       | VCOSEL<2:0>   |             |                       | 0x1F |

|                         | 23:16 | 开路              |                | ICP<2:0>        |            |          | 开路            |             |                       | 0x3F |

|                         | 15:8  | REFCLK 分频器旁路    | REFCLK 分频器复位 B | 开路              |            |          |               | PLL 使能      |                       | 0x40 |

|                         | 7:0   | N<6:0>          |                |                 |            |          | 开路            |             |                       | 0x00 |

|                         |       |                   |         |                 |         |

|-------------------------|-------|-------------------|---------|-----------------|---------|

| 辅助 DAC 控制寄存器(0x03)      | 31:24 | 开路                |         |                 | 0x00    |

|                         | 23:16 | 开路                |         |                 | 0x00    |

|                         | 15:8  | 开路                |         |                 | 0x7F    |

|                         | 7:0   | FSC<7:0>          |         |                 | 0x7F    |

| I/O 更新速率寄存器(0x04)       | 31:24 | I/O 更新速率<31:24>   |         |                 | 0xFF    |

|                         | 23:16 | I/O 更新速率<23:16>   |         |                 | 0xFF    |

|                         | 15:8  | I/O 更新速率<15:8>    |         |                 | 0xFF    |

|                         | 7:0   | I/O 更新速率<7:0>     |         |                 | 0xFF    |

| RAM 段寄存器 0(0x05)        | 47:40 | RAM 地址步进率 0<15:8> |         |                 |         |

|                         | 39:32 | RAM 地址步进率 0<7:0>  |         |                 |         |

|                         | 31:24 | RAM 结束地址 0<9:2>   |         |                 |         |

|                         | 23:16 | RAM 结束地址 0<1:0>   | 开路      |                 |         |

|                         | 15:8  | RAM 起始地址 0<9:2>   |         |                 |         |

|                         | 7:0   | RAM 起始地址 0<1:0>   | 开路      | RAM 回放模式 0<2:0> |         |

| RAM 段寄存器 1(0x06)        | 47:40 | RAM 地址步进率 1<15:8> |         |                 |         |

|                         | 39:32 | RAM 地址步进率 1<7:0>  |         |                 |         |

|                         | 31:24 | RAM 结束地址 1<9:2>   |         |                 |         |

|                         | 23:16 | RAM 结束地址 1<1:0>   | 开路      |                 |         |

|                         | 15:8  | RAM 起始地址 1<9:2>   |         |                 |         |

|                         | 7:0   | RAM 起始地址 1<1:0>   | 开路      | RAM 回放模式 1<2:0> |         |

| 幅度比例因子 (ASF) 寄存器 (0x09) | 31:24 | 幅度斜坡率<15:8>       |         |                 | 0x00    |

|                         | 23:16 | 幅度斜坡率<7:0>        |         |                 | 0x00    |

|                         | 15:8  | 幅度比例因子<13:6>      |         |                 | 0x00    |

|                         | 7:0   | 幅度比例因子<5:0>       |         | 幅度步长<1:0>       | 0x00    |

| 多芯片同步寄存器 (0x0A)         | 31:24 | 同步验证延迟<3:0>       | 同步接收器使能 | 同步发生器使能         | 同步发生器极性 |

|                         | 23:16 | 同步状态预设值<5:0>      |         | 开路              |         |

|                             |       |              |              |      |          |

|-----------------------------|-------|--------------|--------------|------|----------|

| Profile0 寄存器-<br>单音(0x0E)   | 15:8  | 同步发生器延迟<4:0> |              | 开路   | 0x00     |

|                             | 7:0   | 同步接收器延迟<4:0> |              | 开路   | 0x00     |

|                             | 63:56 | 开路           | 幅度比例因子<13:8> |      | N/A      |

|                             | 55:48 |              | 幅度比例因子<7:0>  |      | N/A      |

|                             | 47:40 |              | 相位偏移字<15:8>  |      | N/A      |

|                             | 39:32 |              | 相位偏移字<7:0>   |      | N/A      |

|                             | 31:24 |              | 频率调谐字<31:24> |      | N/A      |

|                             | 23:16 |              | 频率调谐字<23:16> |      | N/A      |

|                             | 15:8  |              | 频率调谐字<15:8>  |      | N/A      |

|                             | 7:0   |              | 频率调谐字<7:0>   |      | N/A      |

| Profile0 寄存器-<br>QDUC(0x0E) | 63:56 | CCI 插值率<7:2> |              | 频谱反转 | 反 CCI 旁路 |

|                             | 55:48 | 输出比例因子       |              |      | N/A      |

|                             | 47:40 | 相位偏移字<15:8>  |              |      | N/A      |

|                             | 39:32 | 相位偏移字<7:0>   |              |      | N/A      |

|                             | 31:24 | 频率调谐字<31:24> |              |      | N/A      |

|                             | 23:16 | 频率调谐字<23:16> |              |      | N/A      |

|                             | 15:8  | 频率调谐字<15:8>  |              |      | N/A      |

|                             | 7:0   | 频率调谐字<7:0>   |              |      | N/A      |

| Profile1 寄存器-<br>单音(0x0F)   | 63:56 | 开路           | 幅度比例因子<13:8> |      | N/A      |

|                             | 55:48 |              | 幅度比例因子<7:0>  |      | N/A      |

|                             | 47:40 |              | 相位偏移字<15:8>  |      | N/A      |

|                             | 39:32 |              | 相位偏移字<7:0>   |      | N/A      |

|                             | 31:24 |              | 频率调谐字<31:24> |      | N/A      |

|                             | 23:16 |              | 频率调谐字<23:16> |      | N/A      |

|                             | 15:8  |              | 频率调谐字<15:8>  |      | N/A      |

|                             | 7:0   |              | 频率调谐字<7:0>   |      | N/A      |

| Profile1 寄存器<br>-QDUC(0x0F) | 63:56 | CCI 插值率<7:2> |              | 频谱反转 | 反 CCI 旁路 |

|                             | 55:48 | 输出比例因子<7:0>  |              |      | N/A      |

|                             |       |              |              |      |          |

|-----------------------------|-------|--------------|--------------|------|----------|

| Profile2 寄存器-<br>单音(0x10)   | 47:40 | 相位偏移字<15:8>  |              |      | N/A      |

|                             | 39:32 | 相位偏移字<7:0>   |              |      | N/A      |

|                             | 31:24 | 频率调谐字<31:24> |              |      | N/A      |

|                             | 23:16 | 频率调谐字<23:16> |              |      | N/A      |

|                             | 15:8  | 频率调谐字<15:8>  |              |      | N/A      |

|                             | 7:0   | 频率调谐字<7:0>   |              |      | N/A      |

|                             | 63:56 | 开路           | 幅度比例因子<13:8> |      |          |

|                             | 55:48 |              | 幅度比例因子<7:0>  |      |          |

|                             | 47:40 |              | 相位偏移字<15:8>  |      |          |

|                             | 39:32 |              | 相位偏移字<7:0>   |      |          |

| Profile2 寄存器-<br>QDUC(0x10) | 31:24 |              | 频率调谐字<31:24> |      |          |

|                             | 23:16 |              | 频率调谐字<23:16> |      |          |

|                             | 15:8  |              | 频率调谐字<15:8>  |      |          |

|                             | 7:0   |              | 频率调谐字<7:0>   |      |          |

|                             | 63:56 | CCI 插值率<7:2> |              | 频谱反转 | 反 CCI 旁路 |

|                             | 55:48 | 输出比例因子<7:0>  |              |      | N/A      |

|                             | 47:40 | 相位偏移字<15:8>  |              |      | N/A      |

|                             | 39:32 | 相位偏移字<7:0>   |              |      | N/A      |

| Profile3 寄存器-<br>单音(0x11)   | 31:24 | 频率调谐字<31:24> |              |      | N/A      |

|                             | 23:16 | 频率调谐字<23:16> |              |      | N/A      |

|                             | 15:8  | 频率调谐字<15:8>  |              |      | N/A      |

|                             | 7:0   | 频率调谐字<7:0>   |              |      | N/A      |

|                             | 63:56 | 开路           | 幅度比例因子<13:8> |      |          |

|                             | 55:48 |              | 幅度比例因子<7:0>  |      |          |

|                             | 47:40 |              | 相位偏移字<15:8>  |      |          |

|                             |       |              |              |  |                   |                   |

|-----------------------------|-------|--------------|--------------|--|-------------------|-------------------|

| Profile3 寄存器<br>-QDUC(0x11) | 15:8  | 频率调谐字<15:8>  |              |  | N/A               |                   |

|                             | 7:0   | 频率调谐字<7:0>   |              |  | N/A               |                   |

|                             | 63:56 | CCI 插值率<7:2> |              |  | 频谱反转 反 CCI 旁路 N/A |                   |

|                             | 55:48 | 输出比例因子<7:0>  |              |  | N/A               |                   |

|                             | 47:40 | 相位偏移字<15:8>  |              |  | N/A               |                   |

|                             | 39:32 | 相位偏移字<7:0>   |              |  | N/A               |                   |

|                             | 31:24 | 频率调谐字<31:24> |              |  | N/A               |                   |

|                             | 23:16 | 频率调谐字<23:16> |              |  | N/A               |                   |

|                             | 15:8  | 频率调谐字<15:8>  |              |  | N/A               |                   |

|                             | 7:0   | 频率调谐字<7:0>   |              |  | N/A               |                   |

| Profile4 寄存器-<br>单音(0x12)   | 63:56 | 开路           | 幅度比例因子<13:8> |  |                   | N/A               |

|                             | 55:48 |              | 幅度比例因子<7:0>  |  |                   | N/A               |

|                             | 47:40 |              | 相位偏移字<15:8>  |  |                   | N/A               |

|                             | 39:32 |              | 相位偏移字<7:0>   |  |                   | N/A               |

|                             | 31:24 |              | 频率调谐字<31:24> |  |                   | N/A               |

|                             | 23:16 |              | 频率调谐字<23:16> |  |                   | N/A               |

|                             | 15:8  |              | 频率调谐字<15:8>  |  |                   | N/A               |

|                             | 7:0   |              | 频率调谐字<7:0>   |  |                   | N/A               |

| Profile4 寄存器-<br>QDUC(0x12) | 63:56 |              | CCI 插值率<7:2> |  |                   | 频谱反转 反 CCI 旁路 N/A |

|                             | 55:48 |              | 输出比例因子<7:0>  |  |                   | N/A               |

|                             | 47:40 |              | 相位偏移字<15:8>  |  |                   | N/A               |

|                             | 39:32 |              | 相位偏移字<7:0>   |  |                   | N/A               |

|                             | 31:24 |              | 频率调谐字<31:24> |  |                   | N/A               |

|                             | 23:16 |              | 频率调谐字<23:16> |  |                   | N/A               |

|                             | 15:8  |              | 频率调谐字<15:8>  |  |                   | N/A               |

|                             | 7:0   |              | 频率调谐字<7:0>   |  |                   | N/A               |

| Profile5 寄存器-<br>单音(0x13)   | 63:56 | 开路           | 幅度比例因子<13:8> |  |                   | N/A               |

|                             | 55:48 |              | 幅度比例因子<7:0>  |  |                   | N/A               |

|                         |       |              |              |      |          |     |

|-------------------------|-------|--------------|--------------|------|----------|-----|

|                         | 47:40 | 相位偏移字<15:8>  |              |      | N/A      |     |

|                         | 39:32 | 相位偏移字<7:0>   |              |      | N/A      |     |

|                         | 31:24 | 频率调谐字<31:24> |              |      | N/A      |     |

|                         | 23:16 | 频率调谐字<23:16> |              |      | N/A      |     |

|                         | 15:8  | 频率调谐字<15:8>  |              |      | N/A      |     |

|                         | 7:0   | 频率调谐字<7:0>   |              |      | N/A      |     |

|                         | 63:56 | CCI 插值率<7:2> |              | 频谱反转 | 反 CCI 旁路 |     |

| Profile5 寄存器-QDUC(0x13) | 55:48 | 输出比例因子<7:0>  |              |      | N/A      |     |

|                         | 47:40 | 相位偏移字<15:8>  |              |      | N/A      |     |

|                         | 39:32 | 相位偏移字<7:0>   |              |      | N/A      |     |

|                         | 31:24 | 频率调谐字<31:24> |              |      | N/A      |     |

|                         | 23:16 | 频率调谐字<23:16> |              |      | N/A      |     |

|                         | 15:8  | 频率调谐字<15:8>  |              |      | N/A      |     |

|                         | 7:0   | 频率调谐字<7:0>   |              |      | N/A      |     |

|                         | 63:56 | 开路           | 幅度比例因子<13:8> |      |          | N/A |

|                         | 55:48 |              | 幅度比例因子<7:0>  |      |          | N/A |

| Profile6 寄存器-单音(0x14)   | 47:40 |              | 相位偏移字<15:8>  |      |          | N/A |

|                         | 39:32 |              | 相位偏移字<7:0>   |      |          | N/A |

|                         | 31:24 |              | 频率调谐字<31:24> |      |          | N/A |

|                         | 23:16 |              | 频率调谐字<23:16> |      |          | N/A |

|                         | 15:8  |              | 频率调谐字<15:8>  |      |          | N/A |

|                         | 7:0   |              | 频率调谐字<7:0>   |      |          | N/A |

|                         | 63:56 | CCI 插值率<7:2> |              | 频谱反转 | 反 CCI 旁路 | N/A |

|                         | 55:48 | 输出比例因子<7:0>  |              |      | N/A      |     |

| Profile6 寄存器-QDUC(0x14) | 47:40 | 相位偏移字<15:8>  |              |      | N/A      |     |

|                         | 39:32 | 相位偏移字<7:0>   |              |      | N/A      |     |

|                         | 31:24 | 频率调谐字<31:24> |              |      | N/A      |     |

|                         | 23:16 | 频率调谐字<23:16> |              |      | N/A      |     |

|                         | 23:16 | 频率调谐字<23:16> |              |      | N/A      |     |

|                         | 23:16 | 频率调谐字<23:16> |              |      | N/A      |     |

|                                                               |       |               |              |      |          |     |

|---------------------------------------------------------------|-------|---------------|--------------|------|----------|-----|

| Profile7 寄存器-<br>单音(0x15)                                     | 15:8  | 频率调谐字<15:8>   |              |      | N/A      |     |

|                                                               | 7:0   | 频率调谐字<7:0>    |              |      | N/A      |     |

|                                                               | 63:56 | 开路            | 幅度比例因子<13:8> |      |          | N/A |

|                                                               | 55:48 |               | 幅度比例因子<7:0>  |      |          | N/A |

|                                                               | 47:40 |               | 相位偏移字<15:8>  |      |          | N/A |

|                                                               | 39:32 |               | 相位偏移字<7:0>   |      |          | N/A |

|                                                               | 31:24 |               | 频率调谐字<31:24> |      |          | N/A |

|                                                               | 23:16 |               | 频率调谐字<23:16> |      |          | N/A |

|                                                               | 15:8  |               | 频率调谐字<15:8>  |      |          | N/A |

|                                                               | 7:0   |               | 频率调谐字<7:0>   |      |          | N/A |

| Profile7 寄存器<br>-QDUC(0x15)                                   | 63:56 | CCI 插值率<7:2>  |              | 频谱反转 | 反 CCI 旁路 | N/A |

|                                                               | 55:48 | 输出比例因子<7:0>   |              |      |          | N/A |

|                                                               | 47:40 | 相位偏移字<15:8>   |              |      |          | N/A |

|                                                               | 39:32 | 相位偏移字<7:0>    |              |      |          | N/A |

|                                                               | 31:24 | 频率调谐字<31:24>  |              |      |          | N/A |

|                                                               | 23:16 | 频率调谐字<23:16>  |              |      |          | N/A |

|                                                               | 15:8  | 频率调谐字<15:8>   |              |      |          | N/A |

|                                                               | 7:0   | 频率调谐字<7:0>    |              |      |          | N/A |

| RAM 寄存器(0x16)<br>GPIO 配置寄存器<br>(0x18)<br>GPIO 数据寄存器<br>(0x19) | 31:0  | RAM 字<31:0>   |              |      | N/A      |     |

|                                                               | 15:0  | GPIO 配置<15:0> |              |      | N/A      |     |

|                                                               | 15:0  | GPIO 数据<15:0> |              |      | N/A      |     |

## 寄存器位功能描述

串行 I/O 端口寄存器地址范围从 0 至 25 (十六进制: 0x00 至 0x19) , 共有 26 个寄存器。但是, 其中有六个寄存器未使用, 所以只有 20 个可用寄存器。未使用的寄存器为 7、8、11 至 13 和 23 (0x07 至 0x08、0x0B 至 0x0D 和 0x17) 。寄存器分配到的字节数各不相同。也就是说, 寄存器具有不同的深度, 其字节容量取决于特定的功能要求。另外, 寄存器主要根据其功能命名。有时候寄存器会基于方便记忆的原则命名。例如, 串行地址 0x00 的寄存器命名为控制功能寄存器 1, 表示为容易记忆的 CFR1。下文详细介绍了芯片寄存器映射中的每一个位的功能。对于由多个位共同实现某一特定功能的情况, 整个位组将视为一个二进制字, 集中加以说明。本节内容按寄存器串行地址顺序组织。每个副标题后是该特定寄存器中各个位的功能描述。寄存器中位的具体位置由<A>或<A:B>表示, 其中 A 和 B 是位编号。<A:B>表示法指定从最高有效位到最低有效位的位范围。例如, <5:2>表示从比特位 5 至 2, 其中由 0 位表示寄存器的 LSB。除非另有说明, 在 I/O 更新置位或者 profile 更改之前, 已编程位不会传输到内部目的位置。

### 控制功能寄存器 1(CFR1)—地址 0x00 此寄存器分配了四个字节。

| 位位    | 引脚名称       | 描述                                                                                                                                                 |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | RAM使能      | 0: 禁用RAM回放功能 (默认)。<br>1: 使能RAM回放功能。                                                                                                                |

| 30:29 | 开路         |                                                                                                                                                    |

| 28    | RAM回放目的位置  | 仅在CFR1<31>=1时有效。<br>0: RAM回放数据路由至基带调整乘法器 (默认)。<br>1: RAM回放数据路由至基带I/Q数据路径。                                                                          |

| 27:26 | 开路         |                                                                                                                                                    |

| 25:24 | 工作模式       | 00: 正交调制模式 (默认)。<br>01: 单音模式。<br>1x: DAC插值模式。                                                                                                      |

| 23    | 手动OSK外部控制  | 仅在CFR1<9:8>=10b时有效。<br>0: OSK引脚无效 (默认)。<br>1: OSK引脚使能手动OSK控制。                                                                                      |

| 22    | 反Sinc滤波器使能 | 0: 反sinc滤波器被旁路 (默认)。<br>1: 反sinc滤波器有效。                                                                                                             |

| 21    | CCI清零      | 串行I/O端口控制器会自动将该位清0。此操作需要数个内部时钟周期才能完成, 在此期间将忽略基带信号链施加于CCI输入端的数据。输入强制为全0, 以清除CCI数据路径, 之后CCI累加器即会复位。<br>0: CCI滤波器正常工作 (默认)。<br>1: 在CCI滤波器中启动累加器的异步复位。 |

| 20:17 | 开路         |                                                                                                                                                    |

| 16    | 选择DDS正弦输出  | 仅在CFR1<25:24>=01b时有效。<br>0: 选择DDS余弦输出 (默认)。<br>1: 选择DDS正弦输出。                                                                                       |

|       |                   |                                                                                                                   |

|-------|-------------------|-------------------------------------------------------------------------------------------------------------------|

| 15:14 | 开路                |                                                                                                                   |

| 13    | 自动清零相位            | 0: DDS相位累加器正常工作 (默认)。<br>1: DDS相位累加器异步、静态复位。                                                                      |

| 12    | 开路                |                                                                                                                   |

| 11    | 清零相位累加器           | 0: DDS相位累加器正常工作 (默认)。<br>1: DDS相位累加器异步、静态复位。                                                                      |

| 10    | 加载ARR@I/O更新       | 0: OSK幅度斜坡率定时器正常工作 (默认)。<br>1: 每次I/O_UPDATE置位或者profile更改后，OSK幅度斜坡率定时器重新加载。                                        |

| 9     | OSK(输出移位键控)<br>使能 | 0: OSK禁用 (默认)。<br>1: OSK使能。                                                                                       |

| 8     | 选择自动OSK           | 仅在CFR1<9>=1时有效。<br>0: 手动OSK使能 (默认)。<br>1: 自动OSK使能。                                                                |

| 7     | 数字部分关断            | 此位无需I/O更新即可生效。<br>0: 数字内核时钟信号有效 (默认)。<br>1: 数字内核时钟信号禁用。                                                           |

| 6     | DAC关断             | 0: DAC时钟信号和偏置电路有效 (默认)。<br>1: DAC时钟信号和偏置电路禁用。                                                                     |

| 5     | REFCLK输入关断        | 此位无需I/O更新即可生效。<br>0: REFCLK输入电路和PLL有效 (默认)。<br>1: REFCLK输入电路和PLL禁用。                                               |

| 4     | 辅助DAC关断           | 0: 辅助DAC时钟信号和偏置电路有效 (默认)。<br>1: 辅助DAC时钟信号和偏置电路禁用。                                                                 |

| 3     | 外部关断控制            | 0: EXT_PWR_DWN引脚置位采用全省电模式运行 (默认)。<br>1: EXT_PWR_DWN引脚置位采用快速恢复省电模式运行。                                              |

| 2     | 自动关断使能            | 在CFR1<25:24>=01b时无效。<br>0: 禁用关断 (默认)。<br>1: 当TxEnable引脚为逻辑0时，基带信号处理链将清除残留数据，同时时钟自动停止。<br>当TxENABLE引脚为逻辑1时，时钟重新启动。 |

| 1     | 仅为SDIO输入          | 0: 配置SDIO引脚进行双向操作；双线式串行编程模式 (默认)。<br>1: 将串行数据I/O引脚(SDIO)仅配置为输入引脚，三线式串行编程模式。                                       |

| 0     | LSB优先             | 0: 配置串行I/O端口为MSB优先格式 (默认)。<br>1: 配置串行I/O端口为LSB优先格式。                                                               |

### 控制功能寄存器 2 (CFR2) — 地址 0x01 (此寄存器分配了四个字节。)

| 位     | 引脚名称                 | 描述                                                                                                                                |

|-------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| 31    | Blackfin接口模式有效       | 仅在CFR1<25:24>=00b (正交调制模式) 时有效。0: 引脚D<17:0>配置为18位并行端口 (默认) 。<br>1: 引脚D<5:4>配置为兼容Blackfin串行接口的双串行端口。引脚D<17:6>和引脚D<3:0>变为16位GPIO端口。 |

| 30    | Blackfin位序           | 仅在CFR2<31>=1时有效。<br>0: 双串行端口(BFI)配置为MSB优先 (默认) 。<br>1: 双串行端口(BFI)配置为LSB优先。                                                        |

| 29    | Blackfin早帧同步使能       | 仅在CFR2<31>=1时有效。<br>0: 双串行端口(BFI)配置为兼容Blackfin晚帧同步操作 (默认) 。<br>1: 双串行端口(BFI)配置为兼容Blackfin早帧同步操作。                                  |

| 28:25 | 开路                   |                                                                                                                                   |

| 24    | 将 Profile 寄存器用作 ASF源 | 仅在CFR1<25:24>=01b (单频调制模式) 且CFR1<9>=0 (OSK禁用) 时有效。<br>0: 幅度比例因子被旁路 (单位增益) 。1: 有效profile寄存器决定幅度比例因子。                               |

| 23    | 内部I/O更新有效            | 此位无需I/O更新即可生效。<br>0: 串行I/O编程与外部I/O_UPDATE引脚置位同步, 该引脚被配置为输入引脚(默认)。<br>1: 串行I/O编程与内部产生的I/O更新信号同步 (内部信号在配置为输出引脚的I/O_UPDATE引脚上产生) 。   |

| 22    | SYNC_CLK使能           | 0: SYNC_CLK引脚禁用; 静态逻辑0输出。<br>1: SYNCCLK引脚产生1/4fSYSCLK时钟信号, 用于同步串行I/O端口 (默认) 。                                                     |

| 21:17 | 开路                   |                                                                                                                                   |

| 16    | 读取有效FTW              | 0: FTW寄存器的串行I/O端口读操作读取FTW寄存器中的内容 (默认) 。<br>1: FTW寄存器的串行I/O端口读操作读取输入DDS相位累加器上的实际32位控制字。                                            |

| 15:14 | I/O更新速率控制            | 仅在CFR2<23>=1时有效。设置参照I/O更新定时器运行分频器的预分频值：<br>00=1分频 (默认) 、01=2分频、10=4分频、11=8分频。                                                     |

| 13    | PDCLK速率控制            | 仅在CFR2<31>=0且CFR1<25:24>=00b时有效。<br>0: PDCLK以输入数据速率工作 (默认) 。<br>1: PDCLK以%输入数据速率工作; 有助于维持并行数据端口上I/Q字和基带信号处理链的内部时钟之间的一致关系。         |

| 12    | 数据格式                 | 0: 施加于引脚D<17:0>的数据字采用二进制补码编码格式 (默认) 。<br>1: 施加于引脚D<17:0>的数据字采用偏移二进制编码格式。                                                          |

|     |            |                                                                                                                                                                                        |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | PDCLK使能    | 0: PDCLK引脚禁用，并强制为静态逻辑0；内部时钟信号会连续运行，为数据分配器提供时序。<br>1: PDCLK引脚上出现内部PDCLK信号（默认）。                                                                                                          |

| 10  | PDCLK反转    | 0: PDCLK正常极性；Q数据与逻辑1有关；!数据与逻辑0有关（默认）。<br>1: PDCLK反转极性。                                                                                                                                 |

| 9   | TxEnable反转 | 0: TxENABLE正常极性；逻辑0表示待机状态，而逻辑1则表示传输状态（默认）。<br>1: TxENABLE反转极性；逻辑0表示传输状态，而逻辑1则表示待机状态。                                                                                                   |

| 8   | Q优先数据配对    | 0: I/Q数据对以!数据优先形式传送，之后是Q数据（默认）。<br>1: I/Q数据对以Q数据优先形式传送，之后是!数据。                                                                                                                         |

| 7   | 匹配延迟使能     | 0: DDS幅度、相位和频率变化同步应用按所列顺序输出（默认）。<br>1: DDS幅度、相位和频率变化同步应用同步输出。                                                                                                                          |

| 6   | 数据分配器保留最后值 | 在CFR1<25:24>=01b时无效。<br>0: 当TxENABLE引脚为逻辑假状态时，数据分配器忽略输入数据，并内部强制基带信号路径为零（默认）。<br>1: 当TxENABLE引脚为逻辑假状态时，数据分配器忽略输入数据，并内部强制保留基带信号路径上收到的最后值。                                                |

| 5   | 同步时序验证禁用   | 0: 使能建立和保持验证电路执行测量；测量结果出现在SYNC_SMP_ERR引脚上；如果该引脚为逻辑1，表示可能正在进行建立/保持验证；而逻辑0则表示未检测到建立/保持验证；在该位设置为逻辑1之前，将一直锁存并保持测量结果。1: 复位建立和保持验证测量电路，强制SYNC_SMP_ERR引脚进入静态逻辑0状态（默认）；在该位恢复到逻辑0状态之前，一直禁用测量电路。 |

| 4:0 | 开路         |                                                                                                                                                                                        |

### 控制功能寄存器 3 (CFR3) — 地址 0x02 (此寄存器分配了四个字节。)

| 位     | 引脚名称           | 描述                                       |

|-------|----------------|------------------------------------------|

| 31:30 | 开路             |                                          |

| 29:28 | DRV0           | 控制 REFCLK_OUT 引脚（详见表 1）；默认值为 01b。        |

| 27    | 开路             |                                          |

| 26:24 | VCO SEL        | 选取 REFCLK PLL VCO 的频段（详见表 2）；默认值为 111b。  |

| 23:22 | 开路             |                                          |

| 21:19 | ICP            | 选取 REFCLK PLL 中的电荷泵电流值（详见表 3）；默认值为 111b。 |

| 18:16 | 开路             |                                          |

| 15    | REFCLK 输入分频器旁路 | 0: 选取输入分频器（默认）。<br>1: 输入分频器被旁路。          |

|      |                  |                                               |

|------|------------------|-----------------------------------------------|

| 14   | REFCLK 输入分频器复位 B | 0: 输入分频器被复位。<br>1: 输入分频器正常工作 (默认)。            |

| 13:9 | 开路               |                                               |

| 8    | PLL 使能           | 0: REFCLK PLL 被旁路 (默认)。<br>1: REFCLK PLL 使能。  |

| 7:1  | N                | 此 7 位数是 REFCLK PLL 反馈分频器的分频模数, 默认值为 0000000b。 |

| 0    | 开路               |                                               |

**辅助 DAC 控制寄存器—地址 0x03 (此寄存器分配了四个字节。)**

| 位    | 引脚名称 | 描述                                                |

|------|------|---------------------------------------------------|

| 31:8 | 开路   |                                                   |

| 7:0  | FSC  | 此8位数用于控制主DAC 满量程输出电流 (参见 “辅助DAC 部分” ) ; 默认值为0xFF。 |

**I/O 更新速率寄存器—地址 0x04 (此寄存器分配了四个字节。此寄存器无需 I/O 更新即可生效。)**

| 位    | 引脚名称     | 描述                                                      |

|------|----------|---------------------------------------------------------|

| 31:0 | I/O 更新速率 | 仅在 CFR2<23> = 1时有效。此32 位数控制自动 I/O 更新速率,默认值为 0xFFFFFFFF。 |

**RAM 段寄存器 0 — 地址为 0x05, 且此寄存器分配了六个字节。此寄存器无需 I/O 更新即可生效。仅在 CFR1<31> = 1 且 RT 引脚上为逻辑 0 至逻辑 1 跃迁时, 此寄存器才有效**

| 位     | 引脚名称      | 描述                                  |

|-------|-----------|-------------------------------------|

| 47:32 | RAM 地址步进率 | 此 16 位数控制 RAM 状态机在指定 RAM 地址范围内的步进率。 |

| 31:22 | RAM 结束地址  | 此 10 位数确定 RAM 状态机的结束地址。             |

| 21:16 | 开路        |                                     |

| 15:6  | RAM 起始地址  | 此 10 位数确定 RAM 状态机的起始地址。             |

| 5:3   | 开路        |                                     |

| 2:0   | RAM回放模式0  | 此3位数确定RAM状态机的回放模式                   |

**RAM 段寄存器 1 — 地址为 0x06, 且此寄存器分配了六个字节。仅在 CFR1<31> = 1 且 RT 引脚上为逻辑 1 至逻辑 0 跃迁时, 此寄存器才有效。**

| 位     | 引脚名称        | 描述                                  |

|-------|-------------|-------------------------------------|

| 47:32 | RAM 地址步进率 1 | 此 16 位数控制 RAM 状态机在指定 RAM 地址范围内的步进率。 |

| 31:22 | RAM 结束地址 1  | 此 10 位数确定 RAM 状态机的结束地址。             |

| 21:16 | 开路          |                                     |

| 15:6  | RAM 起始地址 1  | 此 10 位数确定 RAM 状态机的起始地址。             |

| 5:3   | 开路          |                                     |

|     |          |                   |

|-----|----------|-------------------|

| 2:0 | RAM回放模式1 | 此3位数确定RAM状态机的回放模式 |

|-----|----------|-------------------|

**幅度比例因子(ASF)寄存器** — 地址为 0x09，且此寄存器分配了四个字节。仅在 CFR1<9> = 1 时，此寄存器才有效。

| 位     | 引脚名称  | 描述                                                                                                                                             |

|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | 幅度斜坡率 | 仅在CFR1<8>=1时有效。此16位数控制OSK控制器更新DDS幅度变化的速率。                                                                                                      |

| 15:2  |       | 如果CFR1<8>=0且CFR1<23>=0，那么此14位数是DDS的幅度比例因子。<br>如果CFR1<8>=0且CFR1<23>=1，那么在OSK引脚为逻辑1时，此14位数是DDS的幅度比例因子。<br>如果CFR1<8>=1，那么此14位数设置DDS的最大允许幅度比例因子上限。 |

| 1: 0  | 幅度步长  | 仅在CFR1<8>=1时有效。此2位数控制DDS幅度变化的步长（参见表4）                                                                                                          |

**多芯片同步寄存器** — 地址为 0x0A，且此寄存器分配了四个字节。

| 位     | 引脚名称    | 描述                                                                           |

|-------|---------|------------------------------------------------------------------------------|

| 31:28 | 同步验证延迟  | 默认值为 0000b。此 4 位数设置同步接收器中同步验证模块的 SYSCLK 和延迟 SYNC_IN 信号之间的时序偏斜 (约 150 ps 增量)。 |

| 27    | 同步接收器使能 | 0: 同步时钟接收器禁用 (默认)。<br>1: 同步时钟接收器使能。                                          |

| 26    | 同步发生器使能 | 0: 同步时钟发生器禁用 (默认)。<br>1: 同步时钟发生器使能。                                          |

| 25    | 同步发生器极性 | 0: 同步时钟发生器与系统时钟上升沿一致 (默认)。<br>1: 同步时钟发生器与系统时钟下降沿一致。                          |

| 24    | 开路      |                                                                              |

| 23:18 | 同步状态预设值 | 默认值为 000000b。此 6 位数为内部时钟发生器收到同步脉冲时假定的状态。                                     |

| 17:16 | 开路      |                                                                              |

| 15:11 | 同步发生器延迟 | 默认值为 00000b。此 5 位数设置同步发生器输出延迟 (按约 150 ps 的增量)                                |

| 10:8  | 开路      |                                                                              |

| 7:3   | 同步接收器延迟 | 默认值为 00000b。此 5 位数设置同步接收器输入延迟 (按约 150 ps 的增量)                                |

| 2:0   | 开路      |                                                                              |

## Profile 寄存器

器件的 profile 共使用 8 个连续的串行 I/O 地址 (0x0E 至 0x15)。根据 CFR1<25:24>指定的器件工作模式，这 8 个 profile 寄存器分为单频调制 profile 或 QDUC profile 两种。工作期间，使用外部 PROFILE<2:0>引脚来确定有效 profile 寄存器。单频调制 profile 控制：DDS 频率 (32 位)、DDS 相位偏移 (16 位) 和 DDS 幅度调整 (14 位)。QDUC profile 控制：DDS 频率 (32 位)、DDS 相位偏移 (16 位)、输出幅度调整 (8 位)、CCI 滤波器插值因子、反 CCI 旁路和频谱反转。QDUC profile 还有选择地适用于 DAC 插值工作模式：仅输出调整、CCI 滤波器插值因子和反 CCI 旁路适用；所有其它部分 (DDS 频率、输出幅度调整和频谱反转) 会被忽略。

**Profile<7:0>寄存器 — 单频调制地址为 0x0E 至 0x15，且此寄存器分配了八个字节。**

| 位     | 引脚名称   | 描述                  |

|-------|--------|---------------------|

| 63:62 | 开路     |                     |

| 61:48 | 幅度比例因子 | 此 14 位数控制 DDS 输出幅度。 |

| 47:32 | 相位偏移字  | 此 16 位数控制 DDS 相位偏移。 |

| 31:0  | 频率调谐字  | 此 32 位数控制 DDS 频率    |

**Profile<7:0>寄存器 — QDUC — 地址为 0x0E 至 0x15，且此寄存器分配了八个字节。**

| 位     | 引脚名称     | 描述                                                                                                                                 |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| 63:58 | CCI 插值率  | 此 6 位数是 CCI 滤波器的速率插值因子。                                                                                                            |

| 57    | 频谱反转     | 0: 调制器输出采用以下格式： $I(t) \times \cos(ct) - Q(t) \times \sin(ct)$ .<br>1: 调制器输出采用以下格式： $I(t) \times \cos(ct) + Q(t) \times \sin(ct)$ . |

| 56    | 反 CCI 旁路 | 0: 反 CCI 滤波器使能。<br>1: 反 CCI 滤波器被旁路。                                                                                                |

| 55:48 | 输出比例因子   | 此 8 位数控制输出幅度。                                                                                                                      |

| 47:32 | 相位偏移字    | 此 16 位数控制 DDS 相位偏移。                                                                                                                |

| 31:0  | 频率调谐字    | 此 32 位数控制 DDS 频率。                                                                                                                  |

**RAM 寄存器 — 地址为 0x16，且此寄存器分配了四个字节。**

| 位    | 引脚名称 | 描述                                           |

|------|------|----------------------------------------------|

| 31:0 | RAM字 | 写入RAM的32位字是由RAM段寄存器0或RAM段寄存器1的起始地址和结束地址来定义的。 |

**GPIO 配置寄存器** — 地址为 0x18，且此寄存器分配了两个字节。

| 位    | 引脚名称    | 描述     |

|------|---------|--------|

| 15:0 | GPIO 配置 | 详见表 5。 |

**GPIO 数据寄存器** — 地址为 0x19，且此寄存器分配了两个字节。

| 位    | 引脚名称    | 描述                         |

|------|---------|----------------------------|

| 15:0 | GPIO 数据 | 读或写基于 GPIO 配置寄存器的内容。详见表 5。 |

**表 3 REFCLK\_OUT 缓冲控制**

| CFR3<29:28> | REFCLK_OUT 缓冲 |

|-------------|---------------|

| 00          | 禁用            |

| 01          | 低输出电流         |

| 10          | 中输出电流         |

| 11          | 高输出电流         |

**表 4 VCO 范围位设置**

| VCO SEL 位(CFR3<26:24>) | VCO 范围  |

|------------------------|---------|

| 000                    | VCO0    |

| 001                    | VCO1    |

| 010                    | VCO2    |

| 011                    | VCO3    |

| 100                    | VCO4    |

| 101                    | VCO5    |

| 110                    | PLL 被旁路 |

| 111                    | PLL 被旁路 |

**表 5 PLL 电荷泵电流**

| I <sub>CP</sub> (CFR3<21:19>) | 电荷泵电流 I <sub>CP</sub> (uA) |

|-------------------------------|----------------------------|

| 000                           | 212                        |

| 001                           | 237                        |

| 010                           | 262                        |

| 011                           | 287                        |

| 100                           | 312                        |

| 101                           | 337                        |

| 110                           | 363                        |

| 111                           | 387                        |

**表 6 OSK 幅度步长**

| ASF<1:0> | 幅度步长 |

|----------|------|

| 00       | 1    |

| 01       | 2    |

| 10       | 4    |

| 11       | 8    |

表 7 GPIO 引脚与配置和数据寄存器位

| 引脚标记 | 配置位      | 数据位 |

|------|----------|-----|

| D17  | 15       | 15  |

| D16  | 14       | 14  |

| D15  | 13       | 13  |

| D14  | 12       | 12  |

| D13  | 11       | 11  |

| D12  | 10       | 10  |

| D11  | 9        | 9   |

| D10  | 8        | 8   |

| D9   | 7        | 7   |

| D8   | 6        | 6   |

| D7   | 5        | 5   |

| D6   | 4        | 4   |

| D3   | <b>3</b> | 3   |

| D2   | 2        | 2   |

| D1   | <b>1</b> | 1   |

| D0   | 0        | 0   |

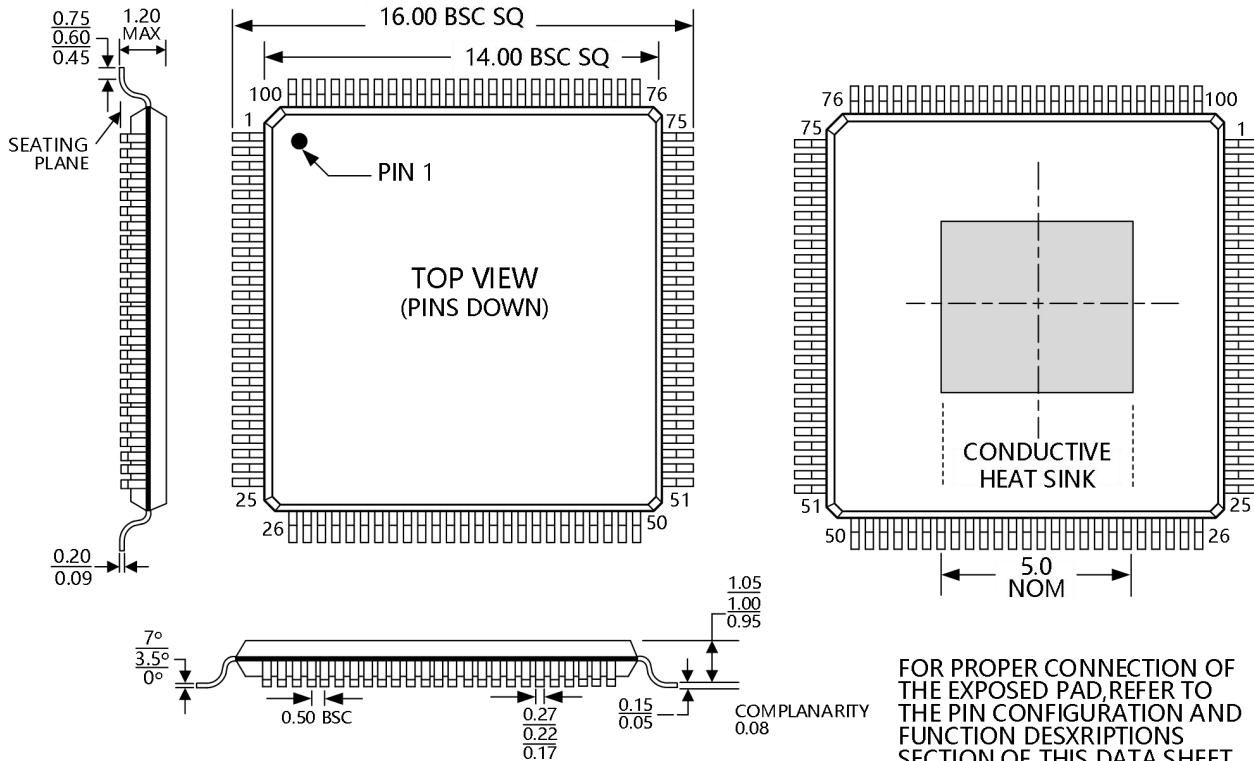

## 封装外形及尺寸

100 引脚裸露焊盘、超薄四方扁平封装[TQFP-100]尺寸(单位:mm)

## 包装/订购信息

| 产品型号       | 温度范围       | 产品封装     | 丝印         | 包装数量   |

|------------|------------|----------|------------|--------|

| CBM99D57BQ | -40°C-85°C | TQFP-100 | CBM99D57BQ | 托盘, 90 |