发布时间:2025-07-30 10:44:15

发布时间:2025-07-30 10:44:15 浏览次数 1746 次

浏览次数 1746 次 在5G基站、宽带传输等场景中,如何用单芯片实现多载波信号的高保真转换?芯佰微CBM97D79TQ作为一款双通道16位高动态范围数模转换器(DAC),凭借1GSPS采样速率、80dBc邻道泄漏比(ACLR)及低功耗特性,成为宽带通信发射链路的核心解决方案。本文从核心性能、设计要点到工程落地,详解其技术优势与实践指南。 一、应用技术背景介绍 在无线通信与宽带传输随着5GNR、WiMax等技术的广泛普及,系统对高带宽、低失真以及多载波并发能力的需求愈发迫切: 带宽需求:5G基站需支持S

在5G基站、宽带传输等场景中,如何用单芯片实现多载波信号的高保真转换?芯佰微CBM97D79TQ作为一款双通道16位高动态范围数模转换器(DAC),凭借1GSPS采样速率、80dBc邻道泄漏比(ACLR)及低功耗特性,成为宽带通信发射链路的核心解决方案。本文从核心性能、设计要点到工程落地,详解其技术优势与实践指南。 一、应用技术背景介绍 在无线通信与宽带传输随着5GNR、WiMax等技术的广泛普及,系统对高带宽、低失真以及多载波并发能力的需求愈发迫切: 带宽需求:5G基站需支持S

在5G基站、宽带传输等场景中,如何用单芯片实现多载波信号的高保真转换?芯佰微CBM97D79TQ作为一款双通道16位高动态范围数模转换器(DAC),凭借1GSPS采样速率、80dBc邻道泄漏比(ACLR)及低功耗特性,成为宽带通信发射链路的核心解决方案。本文从核心性能、设计要点到工程落地,详解其技术优势与实践指南。

在无线通信与宽带传输随着5GNR、WiMax等技术的广泛普及,系统对高带宽、低失真以及多载波并发能力的需求愈发迫切:

带宽需求:5G基站需支持Sub-6GHz频段内多载波信号并行传输,单载波带宽可达100MHz,要求DAC采样速率突破1GSPS以覆盖超宽频谱;

信号保真度:为了确保5G宽带通信信号的质量,邻道泄漏比(ACLR)必须达到或超过80dBc,以避免多载波间的相互干扰,这对数字模拟转换器(DAC)的动态性能提出了极高的要求;

集成与功耗:基站AAU(有源天线单元)等设备受限于体积与散热,这要求DAC不仅具备高集成度,如内置校准和同步功能,还需具备低功耗特性,即功耗需控制在1.0W@1GSPS以下。

此外,在LMDS、MMDS等点对点宽带传输场景中,设备需覆盖1GHz及以上的频段,而传统的多芯片拼接方案面临着同步误差较大、功耗过高的问题,亟须单芯片解决方案实现宽频信号的直接生成。

CBM97D79TQ是芯佰微电子推出的双通道16位高动态范围数模转换器(DAC),它专为宽带通信和无线基础设施而设计,其核心优势在于高采样速率、低功耗以及高度的集成化功能。其核心特性如下:

l 采样速率:支持最高1GSPS采样速率,可生成达奈奎斯特频率的多载波信号,满足宽带通信中“单芯片覆盖多频段”需求。

l 频谱调节能力:内置2×/4×/8×插值器与复数调制器,能将载波灵活放置在DAC带宽内任意位置,无需额外混频器即可适配不同频段需求。

l 数字调制技术:支持实/复调制功能,可直接生成正交调制信号,简化基站发射链路设计。

l 功耗优化:全工作条件下功耗仅1.0W@1GSPS、600mW@500MSPS,适合散热敏感的基站、宽带设备场景。

l 信号保真度:

单载波WCDMA的邻道泄漏比(ACLR)达80dBc@80MHz中频,有效降低对邻道的干扰;

模拟输出电流可调(8.7mA~31.7mA),适配25Ω~50Ω负载,可直接与ADIADL537XFMOD系列调制器对接。

l 可调模拟输出的重要性:

l 输出电流可编程调节(10mA~30mA),允许系统根据负载特性(如25Ω/50Ω阻抗)动态优化信号幅度,避免因固定输出导致的信噪比损失或驱动能力不足。例如,在5G基站中,通过调整输出电流可精确匹配LDMOS功率放大器的输入要求,确保线性度与效率的平衡。

l 辅助校准:4路辅助DAC可直接控制外部VGA的增益与失调,简化前端电路校准流程。

l 多芯片同步:通过差分同步接口(SYNC_I±/SYNC_O±)支持多器件级联,满足MIMO发射分集等多通道扩展需求。

l 时钟管理:内置高性能锁相环(PLL)时钟倍频器,可生成低抖动采样时钟,减少外部时钟源设计复杂度。

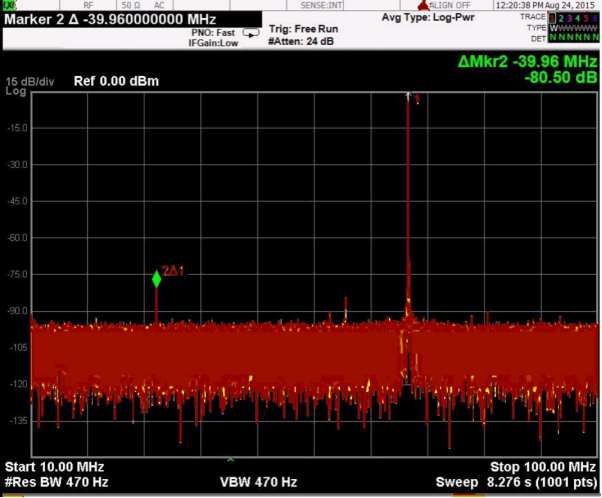

动态性能直接决定信号在传输中的纯净度,实测数据如下:

图1:无杂散动态范围测试结果(中频输出70MHz,转换率800MSPS)

图2:三阶双音互调测试结果(中频输出79MHz/80MHz,转换率400MSPS)

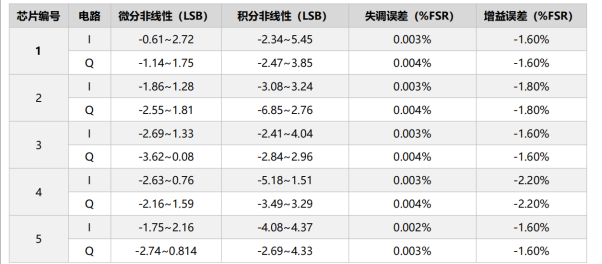

静态参数反映数字信号到模拟信号的线性转换能力,实测5颗芯片的典型值如下:

l 微分非线性(DNL):-0.61~+2.72LSB(I通道),-1.14~+1.75LSB(Q通道);

l 积分非线性(INL):-2.34~+5.45LSB(I通道),-2.47~+3.85LSB(Q通道);

l 失调误差:0.003%FSR(典型值),增益误差-1.6%FSR(典型值)。

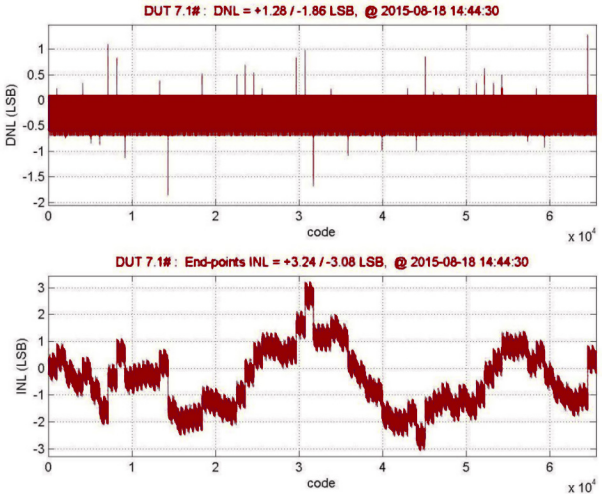

典型微分非线性/积分非线性图

l 工作电压:模拟电源3.3V、数字/时钟电源1.8V,兼容工业级供电场景;

l 工作温度:-40℃~+85℃,满足车载、工业极端环境需求;

l 封装:100引脚TQFP封装(16mm×16mm),托盘包装(90颗/盘)。

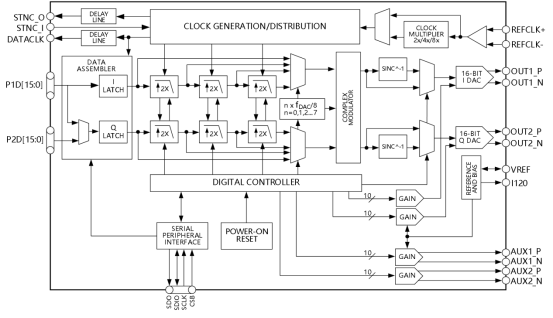

CBM97D79TQ从功能上划分为五大模块:

CBM97D79TQ功能架构框图

l 数字滤波器单元:负责2×/4×/8×插值与数字调制,支持复数调制器将载波灵活放置在DAC带宽内;

l DAC内核单元:16位设计,输出电流可调(10mA~30mA),采用0.18μmCMOS工艺,确保高速转换稳定性;

l 时钟单元:含PLL倍频器,支持外部时钟输入与内部时钟生成,可抑制时钟抖动对动态性能的影响;

l 辅助DAC:2路独立通道,用于外部VGA增益与失调校正,简化模拟前端校准流程;

l 同步单元:多芯片同步单元负责多个芯片间的同步功能。

l 输出匹配:DAC差分输出(OUT1_P/N、OUT2_P/N)需匹配25Ω~50Ω负载,建议通过巴伦转换为单端信号后接入射频链路。例如,在点对点宽带传输中,50Ω匹配可减少反射损耗,提升信号完整性。

l 插值配置:根据输出频率选择插值倍数,例如70MHz输出时推荐4×插值(800MSPS采样),配合数字反sinc滤波器抑制镜像干扰。插值倍数的选择需平衡带宽需求与数字滤波器复杂度。

l 时钟选择:200MSPS及以上采样时可开启内部PLL(PLL_LOCK引脚高电平指示锁定),100MSPS采样时需依赖外部时钟(PLL不支持该频率)。内部PLL在高频下可降低外部时钟源的设计成本。

“要求应用对象电路板的数字地和模拟地尽量分离,不要将数字线布于模拟线旁边或于DAC底下”,需通过0Ω电阻单点连接模拟地(AGND)与数字地(DGND),避免数字噪声耦合至模拟链路。

“芯片的地应该通过尽量多的渠道和足够多的面积与PCB板的地层相连”,需在芯片下方设计大面积敷铜并通过多过孔连接至地层,增强抗干扰能力与散热效果。

“输入连线应尽量短以最小化寄生电容和噪声引入”,尤其时钟(REFCLK±)、同步(SYNC_I±)等高频信号线需短直布线,减少寄生参数影响。

数字数据线(P1D0~P1D15、P2D0~P2D15)不得穿越模拟区域或DAC输出路径下方,避免数字信号干扰模拟链路。

尽管芯片内置静电保护结构,但“测试、搬运、储藏过程中,应注意静电防护”,需采取接地手环、防静电包装等措施,避免高能量电脉冲损坏电路。

l 无线基础设施:W-CDMA、GSM、LTE、5GNR等基站发射链路,支持多载波信号生成。例如,在无线基站中,CBM97D79TQ可直接生成中频信号,驱动LDMOS功率放大器,通过可调输出电流优化偏置电压,确保PA线性度。

l 宽带通信:LMDS、MMDS、点对点宽带传输,单芯片覆盖超宽频段。其1GSPS采样率可支持高达500MHz的信号带宽,满足高速数据传输需求。

l 数字中频合成:直接生成70MHz~200MHz中频信号,省去传统混频器。与ADI ADL537XFMOD调制器配合使用时,可简化射频前端设计。

附件:CBM97D79TQ【中文排版】参数手册