发布时间:2025-08-13 10:25:32

发布时间:2025-08-13 10:25:32 浏览次数 1386 次

浏览次数 1386 次 在雷达、卫星通信等高频信号处理场景中,工程师常面临一个棘手问题:当输入信号频率攀升至400MHz以上时,传统ADC的无杂散动态范围(SFDR)会迅速退化至60dB以下,致使信号中微弱的目标信息被噪声所掩盖——这在卫星通信接收深空微弱信号时,可能直接造成“漏判”或“误判”。 芯佰微电子推出的CBM94AD34-50012位高速模数转换器(ADC),以“高采样率+高动态性能+进口替代兼容性”三大核心优势,成为破解高频信号采集痛点的关键方案。

在雷达、卫星通信等高频信号处理场景中,工程师常面临一个棘手问题:当输入信号频率攀升至400MHz以上时,传统ADC的无杂散动态范围(SFDR)会迅速退化至60dB以下,致使信号中微弱的目标信息被噪声所掩盖——这在卫星通信接收深空微弱信号时,可能直接造成“漏判”或“误判”。 芯佰微电子推出的CBM94AD34-50012位高速模数转换器(ADC),以“高采样率+高动态性能+进口替代兼容性”三大核心优势,成为破解高频信号采集痛点的关键方案。

在雷达、卫星通信等高频信号处理场景中,工程师常面临一个棘手问题:当输入信号频率攀升至400MHz以上时,传统ADC的无杂散动态范围(SFDR)会迅速退化至60dB以下,致使信号中微弱的目标信息被噪声所掩盖——这在卫星通信接收深空微弱信号时,可能直接造成“漏判”或“误判”。

芯佰微电子推出的CBM94AD34-50012位高速模数转换器(ADC),以“高采样率+高动态性能+进口替代兼容性”三大核心优势,成为破解高频信号采集痛点的关键方案。

在雷达、宽带通信等高频应用中,ADC作为“模拟信号转数字信号的第一道关卡”,其性能直接决定后端信号处理的精度。但传统方案存在三大瓶颈:

在高频应用中,ADC的动态性能会显著下降。例如,当输入信号频率从30MHz增加到450MHz时,许多12位ADC的无杂散动态范围(SFDR)会降低8-10dB,这通常会低于65dB的性能阈值。这种性能衰减意味着强信号的旁瓣可能会掩盖较弱的信号,正如在雷达系统中,近距离的强反射目标可能会遮蔽远处的小目标。

采样率与功耗失衡:为覆盖宽带信号,ADC需支持500MSPS以上采样率,但传统方案功耗普遍超过1000mW,在卫星、无人机等供电受限场景中,会导致设备发热严重、续航骤降。

进口替代兼容性差:主流进口ADC(如ADIAD9434)面临交货周期长、供应链不稳定等问题,而国产替代产品常因引脚定义、时序逻辑差异,需重新设计电路板,增加研发成本。

CBM94AD34-500是芯佰微推出的一款12位单片采样模数转换器(ADC),专为高性能、低功耗及易用性优化设计。其采用SiGeBiCMOS工艺制造,封装形式为56引线塑料封装(QFN56),集成采样保持放大器(SHA)和片内基准电压源,可提供完整的信号转换解决方案。VREF引脚支持内部基准电压调节或外部基准输入(外部基准模式需通过SPI端口开启),适配多样化信号处理需求。

该产品主要应用于无线与宽带通信、接收器、通信测试设备、雷达和卫星子系统及功率放大器的线性化等场景。

性能参数:分辨率为12bit,采样率达500MSPS,无杂散动态范围(SFDR)>65dB,输入范围可在1.18Vp-p至1.6Vp-p间调节,且与AD9434系列引脚兼容。

电源与接口:需1.8V模拟电源供电,采用差分时钟以保证整体性能;数字输出兼容LVDS(ANSI-644),数据格式支持二进制补码、格雷码或偏移二进制,配备数据输出时钟确保时序准确。

替代优势:可直接替代美国ADI公司的AD9434BCPZ-500,引脚定义与封装形式一致,便于快速替换。

工作频率(fCLK):≤500MHz

模拟与数字电源电压:1.75V~1.9V

模拟输入共模电压:1.6V~1.8V

工作环境温度:-40℃~85℃

输入信号幅度峰峰值(VIN(P-P)):≤1.5V。

失调误差:-5.0mV~+5.0mV,增益误差:-9%FS~+9%FS

微分线性误差(DNL):-1.5~1.5LSB,积分线性误差(INL):-4.5~4.5LSB

信噪比(SNR):30.3MHz输入时≥63dBFS,450.3MHz输入时≥61dBFS

功耗:典型值≤900mW,待机功耗≤60mW,休眠功耗≤12mW。

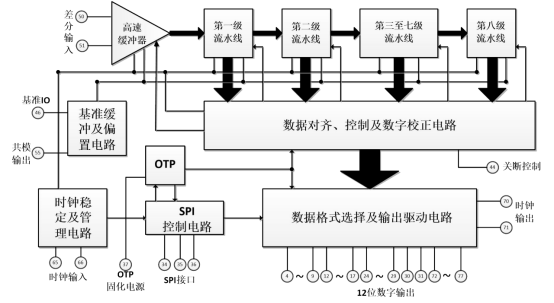

CBM94AD34的功能框图如图1所示,主要包含多级流水线结构(第一级至第八级流水线)、缓冲及偏置电路、基准缓冲电路、数据对齐与控制及数字校正电路、OTP(一次性可编程)电路、时钟稳定及管理电路、控制电路、SPI数据格式选择及输出驱动电路等模块。各模块协同工作,实现从模拟信号到数字信号的高效转换与处理,其中时钟稳定及管理电路确保采样时钟的精准性,SPI接口则为数据格式配置等提供灵活控制。

图1 功能框图

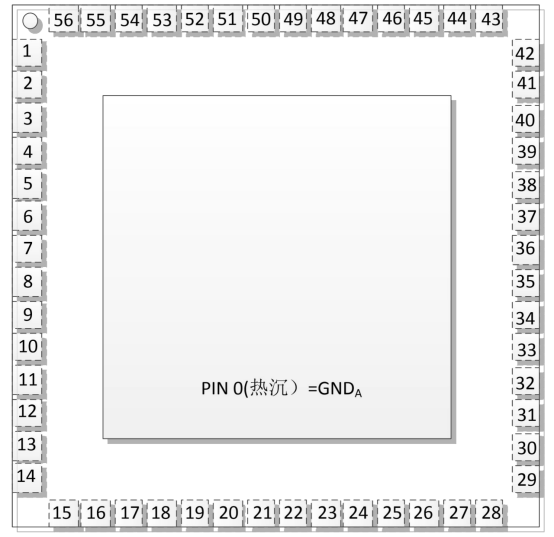

CBM94AD34采用56引脚QFN封装。部分关键引脚功能如下:

图2 引出端排列

差分输出引脚:包括D0-D11的正负端(如1脚D3-、2脚D3+、3脚D4-等),用于输出转换后的数字信号,采用差分形式以提高抗干扰能力。

电源引脚:模拟电源(VCC)分布在多个引脚(如30脚、32脚等),数字电源(VDD)包括7脚、24脚等,均为1.8V供电,需注意模拟电源与数字电源的稳定供电。

控制引脚:29脚PWDN为关断模式选择引脚,25脚SDIO为SPI数据输入/输出(串行模式),26脚SCLK/DFS为SPI时钟(串行模式)/输出数据格式选择(外部引脚模式),27脚CSB为SPI片选(低电平有效),通过这些引脚可实现芯片的模式控制与配置。

输入引脚:35脚VIN+为模拟差分输入正端,36脚VIN-为模拟差分输入负端,44脚CLK+为时钟差分输入正端,45脚CLK-为时钟差分输入负端,40脚CML为共模电压偏置输出。

其他引脚:21脚OR-、22脚OR+为溢出判断位的正负端,49脚DCO-、50脚DCO+为数据时钟的正负端,8脚、23脚、48脚等均为数字地(GNDD)。

注:NC端(如28脚)正常使用时需悬空。

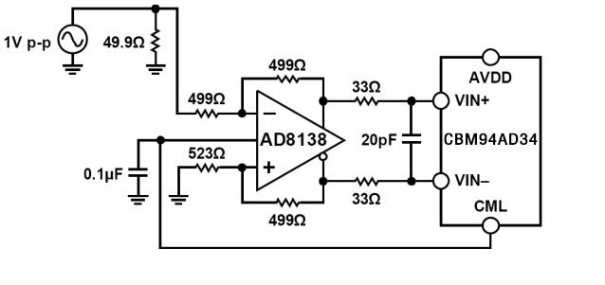

CBM94AD34通过差分输入配置可实现最佳性能,针对不同应用场景有多种推荐电路:

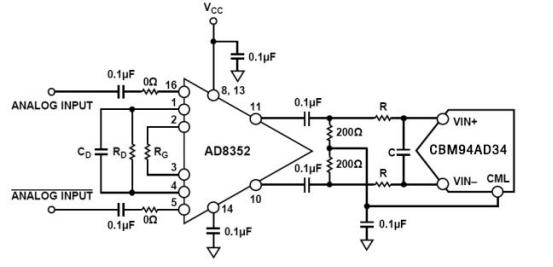

在基带应用中,采用AD8138差分驱动器可提供出色性能和灵活接口。AD8138输出共模电压易设置到AVDD/2+0.5V,且可配置为Sallen-Key滤波器拓扑结构对输入信号进行带宽限制,具体电路如图3所示。

图3 利用AD8138进行差分输入配置

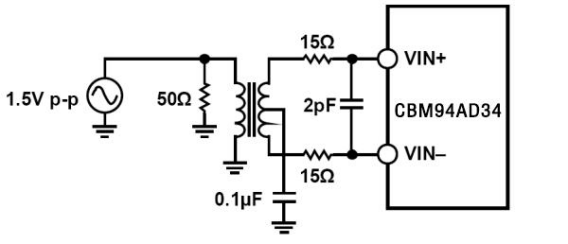

当输入频率处于第二或更高奈奎斯特区域,尤其是70MHz至100MHz的中频欠采样应用时,建议使用差分双巴伦耦合输入配置。选择变压器时需考虑信号特性,避免低频饱和及功率过大导致的失真,电路如图4所示。

图4 差分变压器耦合配置

频率在第二奈奎斯特区域内时,还可使用AD8352差分驱动器,实例电路如图5所示。

图5 利用AD8352进行差分输入配置

在任何配置中,并联电容值C取决于输入频率和源阻抗,可能需要降低电容量或去掉该并联电容。

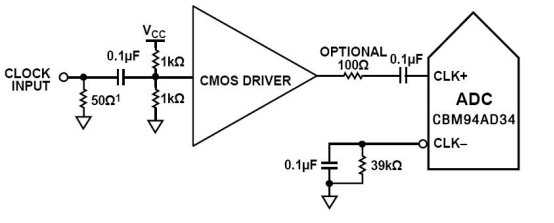

为充分发挥芯片性能,CBM94AD34的采样时钟输入端(CLK+和CLK-)需采用差分信号,推荐以下时钟输入电路:

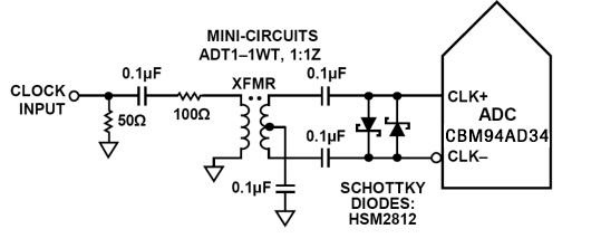

利用射频变压器将低抖动时钟源的单端信号转换为差分信号,跨接在变压器次级上的背对背肖特基二极管可将时钟信号限制为约差分0.8V峰峰值,既保留快速上升和下降时间,又防止大电压摆幅影响低抖动性能,电路如图6所示。

图6 变压器耦合差分时钟配置

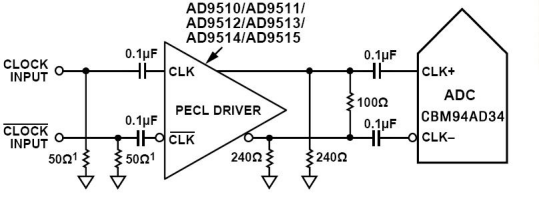

若没有低抖动时钟源,可对差分PECL信号进行交流耦合传输至采样时钟输入引脚,AD9510/AD9511/AD9512/AD9513/AD9514/AD9515系列时钟驱动器具有出色抖动性能,电路如图7所示。

图 7 差分 PECL 采样时钟

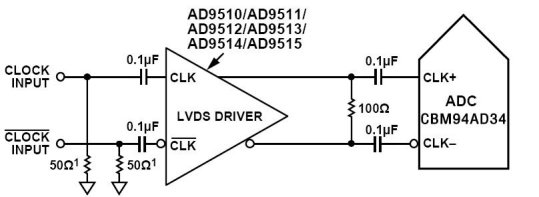

也可采用差分LVDS采样时钟配置,电路如图8所示。

图 8 差分 LVDS 采样时钟

在某些应用中,可利用单端CMOS信号驱动采样时钟输入。CLK+引脚直接由CMOS门电路驱动,CLK-引脚通过0.1uF电容旁路至地;用1.8VCMOS信号驱动CLK+时,需通过0.1uF电容与39k电阻的并联偏置CLK-引脚,电路如图9所示。

图9 单端 1.8 V CMOS 输入时钟

CLK+和CLK-引脚有约0.9V的内部偏置,无需外部偏置;若时钟信号为直流耦合,需使共模电压保持在0.9V范围内。

CBM94AD34的差分输出数据默认符合ANSI-644LVDS标准,数据格式可通过SPI改为低功耗、较少信号选择的类似IEEE1596.3标准的格式,该模式能进一步减少约39mW功耗。LVDS驱动器由一个驱动差分线对的电流源组成,通常电流为3.5mA。在LVDS接收机输入端加100Ω终端电阻,将产生大约350mV的电压摆幅。

该LVDS型输出数据格式有利于与定制ASIC和FPGA中的LVDS接收器连接,在高噪声环境中开关性能优异。建议将带100Ω终端电阻的单一点对点网络拓扑结构放置在离接收器越近越好,避免终端过远或差分布线不良导致的时序错误,且走线长度不超过24英寸,差分输出走线需并行且长度相同。

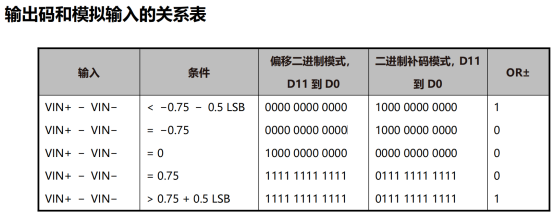

输出数据格式默认为偏移二进制,也支持二进制补码、格雷码等,输入与输出码及模拟输入的关系如表所示。

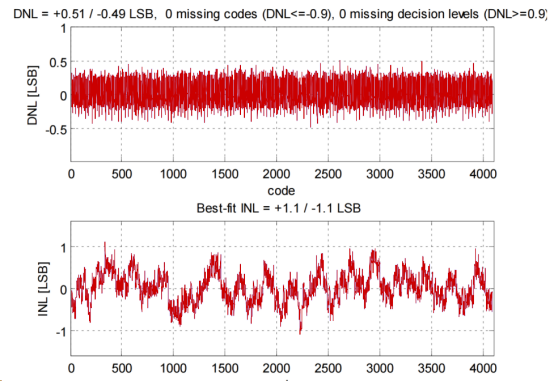

在采样率fCLK=500MHz、输入信号频率fIN=30.3MHz的测试条件下,CBM94AD34的微分线性误差(DNL)为-0.51/+0.49LSB,无丢失码(DNL≤-0.9)和丢失判决电平(DNL≥0.9);积分线性误差(INL)为-1.1/+1.1LSB。

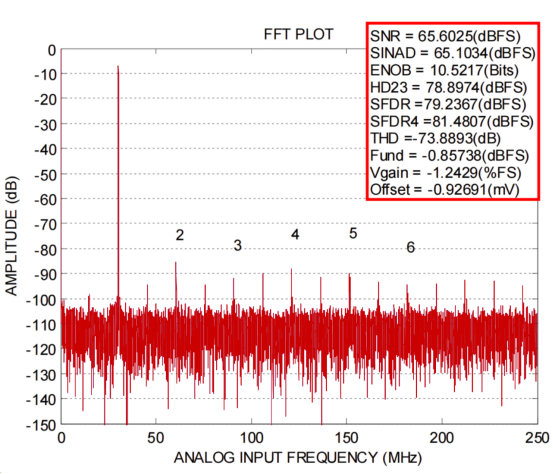

当采样率fCLK=499.99970304MHz、输入信号频率fIN=30.28867830MHz时,测试结果为:SFDR=79.23dBFS,二阶和三阶谐波失真(HD2,3nd)=78.89dBFS,四阶谐波失真(HD4nd)=81.48dBFS,SNR=65.6dBFS,SINAD=65.1034dBFS,ENOB=10.5217bits。

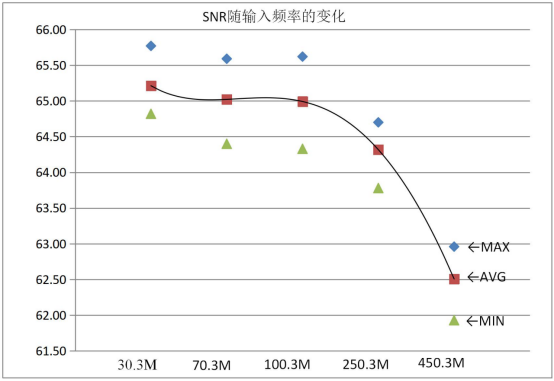

根据CBM94AD34模数转换器的性能参数,其在宽带应用中具有良好的动态性能表现,SNR随输入频率的变化曲线,在30.3MHz、70.3MHz、100.3MHz、250.3MHz、450.3MHz等输入频率点呈现一定变化,整体保持在较高水平。

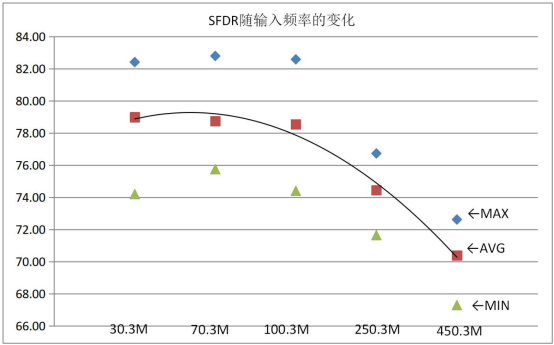

SFDR随输入频率的变化曲线表明,在各种输入频率条件下,无杂散动态范围均展现出卓越的性能,充分满足宽带应用的各种需求。

在无线与宽带通信系统中,CBM94AD34500MSPS的采样速率可满足宽带信号的实时数字化需求,12位分辨率与≥65dB的SFDR(无杂散动态范围)能精准捕获复杂调制信号的细节特征,适配基站收发信机、卫星通信地面站等设备的信号采集需求。

作为接收器核心组件,CBM94AD34的宽输入范围(1.18Vp-p至1.6Vp-p)可兼容不同强度的接收信号,差分输入架构与抗干扰设计(LVDS输出、差分时钟)能有效抑制噪声,确保对微弱信号(如远距离通信信号、雷达回波)的准确转换,广泛用于各类通信接收器、雷达接收前端等场景。

针对雷达和卫星子系统,CBM94AD34的高动态性能(SFDR≥72dBFS@30.3MHz)能区分强弱目标信号,-40℃~85℃的宽温工作范围可适应极端环境,差分时钟设计保证高速采样的时序稳定性,在气象雷达、相控阵雷达及星载数据传输系统中发挥关键作用。